United States District Court, D. Delaware.

#### **BELL COMMUNICATIONS RESEARCH, INC,**

Plaintiff. v. **FORE SYSTEMS, INC,** Defendant.

No. CIV.A. 98-586-JJF

Aug. 29, 2000.

Owner of patents for multiplexing and demultiplexing digital data streams sued competitor for infringement. Construing claims language, the District Court, Farnan, J., held that: (1) preamble for multiplexing patent did not require that method steps all be performed at single transmitting device; (2) bit streams involved could be created in either serial or parallel configuration; (3) multiplexing patent required two or more empty data frames to be filled at same time by different data sources; (4) preamble for demultiplexing patent limited it to taking of multiplexed data frames, interleaved without gaps or pauses, and separating them into their original, single, data frames, each of which had exactly same format; and (5) demultiplexing patent required that bit patterns from two or more adjacent reconstructed bytes be compared with bit patterns known to have been present in two or more adjacent bytes in each of the contributory frames which had been multiplexed to form received bit stream.

Claims construed.

4,835,768, 4,893,306. Construed.

Richard K. Herrmann, Esquire, Mary B. Matterer, Esquire, Dale R. Dube, Esquire of Blank Rome Comisky Mccauley L.L.P., Wilmington, Delaware. Of counsel: Donald Dunner, Esquire, Vincent P. Kovalick, Esquire, Richard H. Smith, Esquire, Frank A. DeCosta, III, Esquire, Houtan K. Esfahani, Esquire of Finnegan, Henderson, Farabow, Garrett & Dunner, L.L.P., Washington, D.C. Attorneys for Plaintiff and Counter-defendant, Bell Communications Research, Inc.

William J. Marsden, Jr., Esquire of Fish & Richardson P.C., Wilmington, Delaware. Of counsel: John E. Gartman, Esquire, Christopher S. Marchese, Esquire, Amar L. Thakur, Esquire, Todd G. Miller, Esquire of Fish & Richardson P.C., San Diego, California. Attorneys for Defendant and Counter-plaintiff, Fore Systems, Inc.

#### **OPINION**

#### FARNAN, District Judge.

This action was brought by Plaintiff, Bell Communication Research, Inc. ("Bellcore") against Defendant Fore, Systems, Inc. ("FORE") alleging infringement of United States Patent Nos. 4,893,306 (the " '306 Patent"); 4,835,768 (the " '768 Patent"), 4,740,954 (the " '954 Patent") and 4,706,080 (the " '080 Patent"). The issue currently before the Court is the claim construction of the patents in suit. The parties briefed their respective positions on claim construction, and the Court held a *Markman* hearing on March 23, 2000. Thereafter, on August 1, 2000, the parties stipulated to the dismissal of Bellcore's claims under the '080 and '954 Patents (D.I.340) leaving only the disputed portions of the '306 and '768 Patents for the Court's claim construction. This Opinion presents the Court's constructions of the disputed terms in the '306 and '768 Patents. FN1

FN1. For ease of reference, the Court has attached the full text and accompanying figures of the '306 and '768 Patents to this Opinion.

## BACKGROUND

#### I. Introduction to the Technology Generally

The '306 and '768 Patents relate to telecommunications technology. A telecommunicationsnetwork can accept input from various sources like speech from a telephone, data from a computer, or a video signal from a camera. In today's telephone network system, voice signals are converted into "digital" signals by analog-digital converters. A digital signal represents information in a binary form or "bit." A bit can have a value of "1" or "0." Bits are typically transmitted between telephone switches in parallel groupings of eight bits known as "bytes."

Like telephones, computers are also connected by networks which utilize this transmission process. Small localized networks like those used by single business entities are called "Local Area Networks" or "LANs." LANs can be connected together by computers called "routers" or "bridges" to form larger networks typically referred to as "WANs" or "Wide Area Networks."

## **II.** The Patents

The '306 and '768 Patents relate to transmission systems. Specifically, they are concerned with how a series of bits traveling down a physical wire are grouped and packaged by the sending source for transmission and how they are ungrouped and unpackaged by the receiving source.

## A. The '306 Patent

The '306 patent describes a digital network transport system known as Dynamic Time Division Multiplexing ("DTDM"). In a DTDM network, the fundamental unit of data transport is known as a frame. Each frame contains two fixed length fields, an overhead and a payload. The overhead field contains information such as the empty/full status of the frame and information related to timing. The payload field of the frame may be filled with a data packet, which contains information and a header field. The header field serves a similar purpose to the address on a mailing envelope. Stated another way, each occupied frame contains a transmission overhead field, a header field, and an information field.

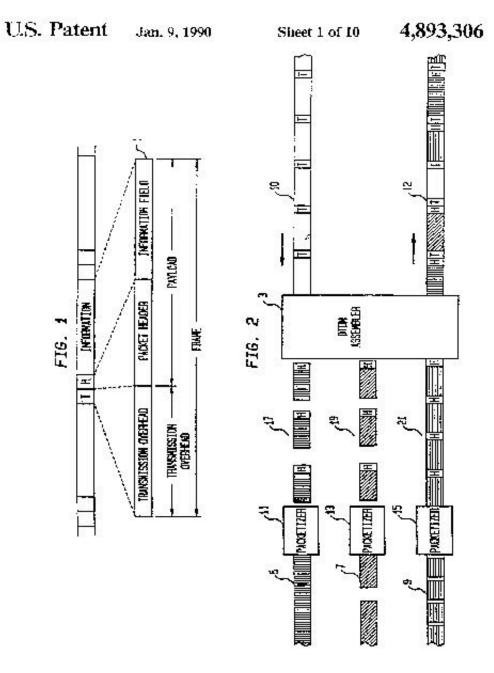

Figure 2 of the '306 Patent represents the assembly of the DTDM bit stream. A "train" of DTDM frames 10

with empty payload fields is generated. This train has a transmission or bit rate that serves as the basic backbone transmission rate for the system. The assembler 3 inserts data from different sources known as tributaries into the train 10. In Figure 2, items 5, 7 and 9 represent three different tributaries or information input streams, each being transmitted from a different source and at a different rate of speed. For example, stream 5 might originate from a telephone, stream 7 from a computer, and stream 9 from a video camera. Before this information can be inserted into stream 10, the packetizers (11, 13, and 15) each take their respective input stream and break them up into fixed length packets of data and attach a packet header (H). The completed process is shown in Figure 2 by items 17, 19 and 21.

The packets that comprise streams 17, 19 and 21 are inserted into the empty payload fields of the frames in stream 10. The end result, represented by stream 12, is a stream of data at a single transmission rate that has multiplexed information received from three different sources at three different transmission rates.

## B. The '768 Patent

The '768 Patent relates to a circuit and technique for recognizing and identifying information transported in a transmission bit stream. The '768 Patent discusses the invention in terms of fiber optic transmission systems. Fiber optic transmission systems utilize optical fibers to carry great amounts of information at the speed of light. As explained previously, this information is transmitted in the form of bits. In order for computers to understand how to read the bits it receives as a bit stream, communications designers organize the bits into predetermined patterns or structures. The patterns or structures for organizingbits and the rules for interpreting them are known as "protocols."

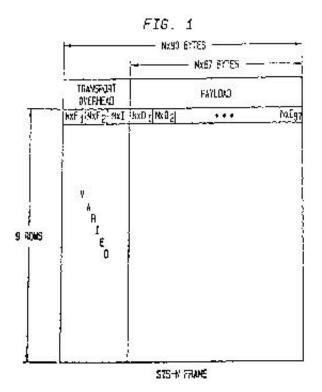

One protocol used for fiber optics transmission is called SONET (Synchronous Optical Network). The basic SONET structure or "frame" consists of nine rows of ninety data bytes. Of the ninety bytes in each row, 3 bytes are transport overhead information and 87 bytes are payload information. The first two bytes of transport overhead, identified in the '768 Patent as F1 and F2, are framing bytes which can be recognized by a receiver to synchronize the receiving circuits to the SONET frame structure. The F1 and F2 bytes have distinct bit patterns which are always the same.

A SONET frame is transmitted row by row as a sequential bit stream beginning with the first F1 byte in row one through the last payload byte in row one, followed by the first overhead byte in row two through the last payload byte in row two, and so forth. The process continues byte by byte and row by row until the entire frame has been transmitted.

Although the basic SONET frame ("STS-1") permits the fast transmission of information, this transmission is not fast enough for some applications. To facilitate even faster transmission of information, the SONET designers wrote protocols for forming larger frames which are basically multiples of the basis SONET STS-1 frame. For example, an STS-3 frame is formed by combining three STS-1 frames, and an STS-12 frame is formed by combining four STS-3 frames. Although an STS-3 frame carries three times as much information at three times the bit rate of an STS-1 frame, the STS-3 frame is transmitted at the same frame rate. The creation of these larger frames using multiples of the basic STS-1 frame is known as the SONET multiplexing hierarchy.

The '768 Patent relates to a technique for recognizing and reconstructing the bytes from a bit stream generated in accordance with the SONET hierarchy. When a computer receives a bit stream, it must reconstruct and identify each frame in order to retrieve the data being transported. For example, the

computer must identify the F1 byte to synchronize itself to the beginning of the frame. Once the beginning of the frame is located, the frame boundaries can be located by counting bytes.

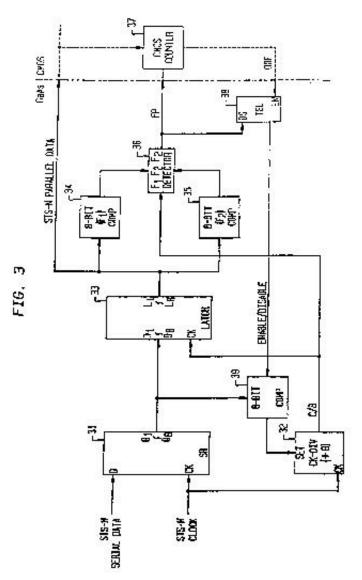

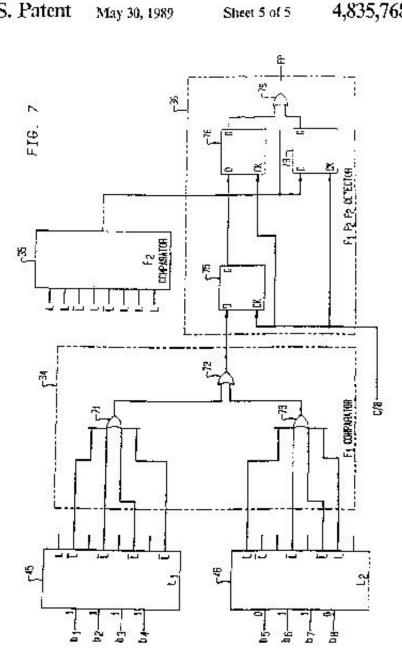

The '768 Patent provides a fast method for recovering bytes and identifying and synchronizing to frame boundaries. The invention in the '768 Patent provides for a shift register that accumulates the serially-received bits and holds a byte of data. A bit comparator compares the accumulated bits with the known bit pattern for the F1 byte. When the accumulated bits match the known pattern for the F1 byte the comparator generates a signal. Circuits respond to the first signal by outputting the F1 byte and each subsequently received byte. The sequence of byte signals generated by the comparator represents the reconstructed bytes of the originally transmitted frame.

In order to ascertain the frame boundaries, additional comparing circuits compare output bytes to the known byte patterns for the F1 and F2 bytes. The circuitry is basically looking for a transition from F1 type bytes to F2 type bytes or the sequence F1, F2, F2. When the circuitry detects the change a second signal ("FP") is generated. This second signal is the benchmark from which the frame boundaries are determined. Because the receiver knows the STS-N level of the incoming bit stream, it also knows at what byte of the frame the transition from F1 to F2 occurred. The receiver then knows when the first byte of the next frame will be received by counting the bytes following the F1 to F2 transition.

When complete frame synchronization is achieved, the comparator is disabled by a toggle, so that the system won't shift the byte boundaries by any subsequent errors in the F1 pattern. If the second signal does not occur for a number of consecutive frames, an out of frame signal ("OOF") is generated and the toggle turns the comparator back on to search for the F1 pattern again.

#### DISCUSSION

## I. The Legal Principles of Claim Construction

[1] [2] [3] [4] [5] Claim construction is a question of law. Markman v. Westview Instruments, Inc., 52 F.3d 967, 977-78 (Fed.Cir.1995), *aff'd*, 517 U.S. 370, 388-90, 116 S.Ct. 1384, 134 L.Ed.2d 577 (1996). When construing the claims of a patent, a court considers the literal language of the claim, the patent specification and the prosecution history. Markman, 52 F.3d at 979. A court may consider extrinsic evidence, including expert and inventor testimony, dictionaries, and learned treatises, in order to assist it in construing the true meaning of the language used in the patent. Id. at 979-80 (citations omitted). A court should interpret the language in a claim by applying the ordinary and accustomed meaning of the words in the claim. Envirotech Corp. v. Al George, Inc., 730 F.2d 753, 759 (Fed.Cir.1984). However, if the patent inventor clearly supplies a different meaning, the claim should be interpreted accordingly. Markman, 52 F.3d at 980 (noting that patentee is free to be his own lexicographer, but emphasizing that any special definitions given to words must be clearly set forth in patent). If possible, claims should be construed to uphold validity. In re Yamamoto, 740 F.2d 1569, 1571 & n. \* (Fed.Cir.1984) (citations omitted).

[6] Before turning to the patents at issue in this dispute, the Court is compelled to address what it perceives to be a potential problem regarding the claim construction issues in this case. Throughout their briefs, the parties raise terms or phrases for claim construction which are either not responded to by the opposing party or are rebutted by the opposing party without sufficient explanation and/or without advancing a counter-proposal for construction. In its Opposition Markman Brief, FORE acknowledges this issue and indicates that it will not engage in claim interpretation for the sake of "achieving linguistic purity and absolute hypothetical precision on every word." (D.I. 153 at 1). FORE also states that "[t]o the extent that Bellcore's

definitions do not affect the issues in this case, they are an advisory and needless exercise in claim interpretation-and should be rejected." (D.I. 153 at 1-2). The Court agrees that claim interpretation should involve only genuinely disputed terms that impact infringement or validity issues. This having been said, the Court declines to adopt constructions for terms and/or phrases raised by only one party and either not addressed by the other party or not responded to with sufficient information and/or a counter-proposal for claim construction. However, if after joint consultation between the parties, one party still genuinely believes that additional terms or phrases impact infringement or validity and require construction, the Court will require the party to submit a letter memorandum, no more than 3 pages in length (with customary margins and font size), stating the terms in need of construction, the proposed constructions, and the reasons for the construction. The opposing party is then required to submit a response letter, no more than 3 pages in length (with customary margins and font size), indicating their position, i.e. whether they concede to the definitions and if not, offering alternative proposed constructions and the reasons for the proposed constructions. In permitting the parties this opportunity, the Court wishes to make clear that these letter memoranda shall not reargue constructions which have been decided in this Opinion and shall not raise terms or phrases which were not previously raised by a party in the previous sets of claim construction briefing. With this understanding, the Court will proceed to construe the disputed terms of the '306 and '768 Patents.

## II. The Meaning Of The Disputed Terms of the '306 and '768 Patents

## A. The '306 Patent

Bellcore asserts Claims 1, 3 and 4 of the '306 patent. The Court will address the disputes relevant to each claim in turn.

## 1. Claim 1 of the '306 Patent

In full, Claim 1 of the '306 Patent provides:

A method for simultaneously transmitting data from sources having different bit rates in a telecommunication network comprising the steps of:

generating a bit stream comprising a sequence of frames, each of said frames including a transmission overhead field containing frame timing information and an empty payload field, and

filling the empty payload fields in said frames with data in packetized format from a plurality of sources which have access to the bit stream including circuit or packet sources, such that data in packetized format from any of said sources is written into any available empty payload field of any of said frames for transmitting data from each of said sources at its own desired bit rate via said bit stream and for transmitting data from said plurality of sources simultaneously via said bit stream.

The Court will examine each of the disputed terms and phrases below.

## a. A method for simultaneously transmitting data from sources having different bit rates in a telecommunication network comprising the steps of:

[7] Bellcore contends that the language "[a] method for simultaneously transmitting data from sources having different bit rates in a telecommunication network" means that the method steps are performed at one

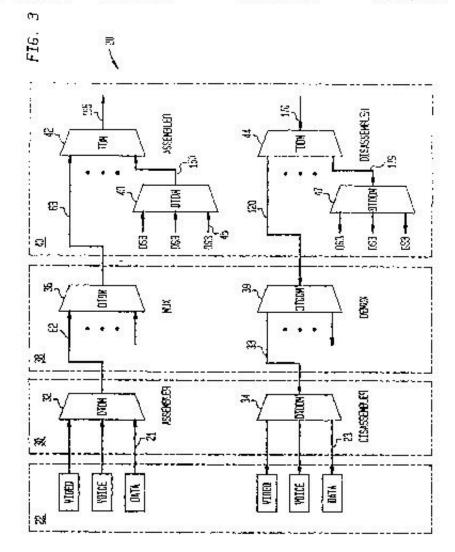

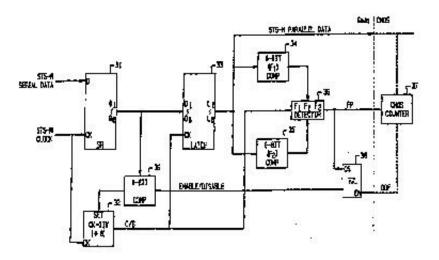

transmitting device. (D.I. 142 at 24-25; D.I. 144 at 10). According to Bellcore, the transmitting device simultaneously transmits data from more than one source in the telecommunications network connected to that transmitting device. In support of its position, Bellcore directs the Court to the conceptual illustrations depicted in Figures 2 and 3 of the '306 Patent. For example, Bellcore points out that the DTDM assembler 32 shown in Figure 3 performs both the generating and filling steps of the method and transmits frames on transmission line 62, which is part of a telecommunications network. In addition, Bellcore relies on language in the specification which provides, for example, that "the DTDM system, packet and circuit traffic can be multiplexed through the same multiplexer." ('306 Patent, col. 4, lines 65-66; col. 5, lines 13-15).

In addition to the figures and language of the specification, Bellcore also directs the Court to the prosecution history of the '306 Patent. According to Bellcore, the applicants amended Claim 1 of the '306 Patent to distinguish prior art known as the Shikama et al. reference. (D.I. 143, Ex. J at A114-A117). Bellcore contends that in the Shikama reference frames are generated in one device in one network and data added to those frames at other devices in the network, but in the '306 Patent the method steps must be performed at one transmitting device which simultaneously transmits data from more than one source in the telecommunications network connected to that transmitting device.

In response to Bellcore's proffered interpretation of the preamble language as requiring the methods steps to be performed at one transmitting device, FORE contends that neither the claim language nor the specification supports Bellcore's attempt to import the limitation of "one transmitting device" into the claim. In other words, FORE does not limit the language to require the acts to be performed at one transmitting device. (D.I. 153 at 2-4). FORE points out that the only conceivable structure mentioned in the plain language of this clause is the word "sources" and that this word says nothing about only "one transmitting device." FORE also contends that the figures shown in the patent specification show multiple devices and not one device. Thus FORE's proffered construction of this phrase is that the acts simply be performed in accordance with all the recited steps in the patent.

After reviewing the claim language, specification and prosecution history of the '306 Patent in light of the parties' respective positions, the Court agrees with FORE's interpretation of this language. Although the specification suggests that the method steps listed after the preamble *may* be performed using a single transmitting device, there is nothing in the claim language, specification or prosecution history *requiring* that the method be accomplished by a single transmitting device. For example, the language of the claim does not refer to a single device. Moreover, the very language cited by Bellcore in the specification provides that the DTDM system, packet and circuit traffic "can" or "may" be multiplexed through the same multiplexer, not that it "must" be multiplexed through the same multiplexer. Accordingly the Court construes the preamble language "[a] method for simultaneously transmitting data from sources having different bit rates in a telecommunication network comprising the steps of" to require that the acts be performed in accordance with the subsequently recited steps in the claim, and the Court declines to limit this phrase to require the method steps to be performed at one transmitting device.

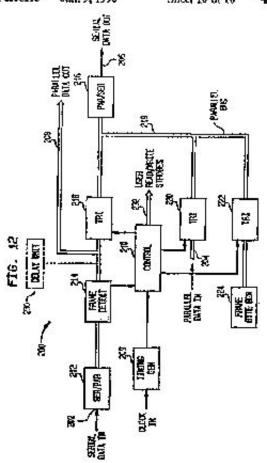

#### b. generating a bit stream

[8] The crux of the parties' dispute concerning the phrase "generating a bit stream," is whether this language encompasses a stream in only serial configuration or a stream in either serial or parallel configuration. Bellcore contends that this language means generating bits or bytes at particular time intervals. (D.I. 142 at 25). Thus, according to Bellcore, the "bit stream" can be either a serial bit stream or a parallel bit stream that is "byte wide." In support of its position, Bellcore directs the Court to the preferred embodiment shown

in Figure 12 of the '306 Patent. (D.I. 151 at 7-8; D.I. 142 at 25-27).

Figure 12 illustrates the framer circuitry performing the generating step by originating and processing data as a parallel bit stream (in byte format-multiple bits at one time). Bytes are transmitted between framers in a serial bit stream. In the language of the specification

The framer unit 200 may also be utilized to generate a chain of empty DTDM packets [sic] (see e.g., framer 52 in FIG. 4). In this case the serial input 202 and associated serial-to-parallel converter 212 are not utilized. Instead, the control 210 applies a periodic signal to tristate 222 so that a frame alignment word is periodically read from *frame byte ROM 224* and *transmitted via bus 219 to parallel-to-serial converter 216* and serial output 206 so as to define a train of empty DTDM frames.

('306 Patent col. 16, line 63-col. 17, line 2) (emphasis added).

An examination of Figure 12 shows a single line used where serial data is present, for example item 206, and a double line used where parallel data is represented, for example item 219. Therefore, Bellcore argues, to construe the phrase generating a bit stream to encompass only a serial configuration would exclude the preferred embodiment set out in Figure 12. (D.I. 151 at 7).

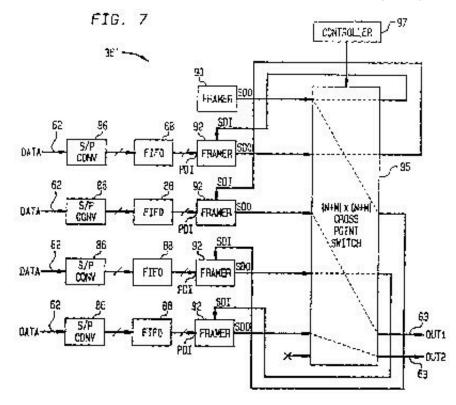

In response to Bellcore's interpretation, Fore contends that "generating a bit stream" means creating a serial configuration of bits, or stated another way, a continuous line of bits sent one at a time from one point to another. To this effect, FORE contends that a "bit stream" is not a "byte stream." (D.I. 153 at 5-6; D.I. 146 at 10-11). In support of its position, FORE directs the Court to Figure 3 of the '306 Patent and its accompanying text in the specification which provides that:

the DTDM bit stream leaves the *serial* data output of framer (sdo) of framer unit 52 and enters the *serial* data input of the top most framer unit 53. The DTDM bit stream leaves the topmost framer 53 via its *serial* data output (sdo). The DTDM bit stream then enters the *serial* data input (sdi) of each succeeding framer unit and leaves via the *serial* data output (sdo) of each framer unit.

('306 Patent, col. 8, lines 62-66 (emphasis added)).

In addition to Figure 3, Fore also contends that the preferred embodiment in Figure 12 and its accompanying text supports its claim interpretation. Fore contends that while it is possible that bytes may be used internally in transmission equipment (D.I. 146 at 10), the frames generated and sent over transmission lines are in a serial bit configuration, as evidenced by the fact that the portion of the specification describing Figure 12 states that the empty DTDM frames are defined by sending data to parallel-to-serial converter 216 and then to serial output 206.

Additionally, FORE directs the Court to that portion of the specification describing bit stream rates. According to FORE, the specification describes bit stream rates in terms of megabits per second, confirming that a bit stream is a serial configuration of bits and not a parallel byte wide configuration. (D.I. 153 at 5, citing '306 patent, col. 2, lines 25-35; col. 5, lines 13-22).

The Court disagrees with FORE's interpretation that the phrase "generating a bit stream" is limited to a serial configuration of bits. First, there is nothing in the plain language of the claim limiting a "bit stream" to a "serial bit stream." Indeed, the claim does not utilize the modifying or limiting word "serial" in

describing the "bit stream." While it is true that the language used is "bit stream" and not "byte stream," it is also true that a byte is composed of bits. Therefore, the Court cannot conclude that the use of the word bit excludes eight bits in parallel, otherwise known as a byte.

With regard to FORE's argument that the specification refers to bit stream rates in terms of megabites per second, the Court is unpersuaded. The lines cited by FORE refer to rates measured in both Mb/sec and Mbit/sec, suggesting that Mb/sec might well mean megabytes per second.

As for Figure 12 and its accompanying text, the Court concludes that these references support Bellcore's position that the bit stream generated internally in the framer circuit begins in a parallel state and is then converted to a serial state before transmission. Accordingly, the Court concludes that the phrase "generating a bit stream" encompasses the creation of either serial or parallel bit streams.

#### c. frame timing information

[9] Bellcore argues that "frame timing information" should be construed to mean frame alignment information. (D.I. 144 at 11; D.I. 142 at 27; D.I. 151 at 8). According to Bellcore, the frame timing information permits a receiver to identify the start of a frame and synchronize to the frame boundaries. (D.I. 142 at 27). In support of its proposed construction, Bellcore cites language from the specification stating: "[t]he overhead field includes, for example, *a frame alignment word for frame timing* and the empty/full status of the frame" ('306 Patent, col. 4, lines 52-54 (emphasis added)) and "[t]he following information may be available in the overhead field of every frame, *frame alignment word for frame timing* ...." ('306 Patent, col. 6, lines 61-64 (emphasis added)).

Fore contends that "frame timing information should be construed to mean one or more bits that indicate the beginning of a frame." (D.I. 144 at 12; D.I. 146 at 11). Fore characterizes the question before the Court as whether "frame timing information" must be more than one bit, as Bellcore contends, or may it be one or more bits, as FORE contends. (D.I. 146 at 11). As for Bellcore's reliance on the specification's use of the phrase "frame alignment word" in discussing "frame timing," FORE contends that a "word" is composed of one or more bits just as a "word" in the English language is composed of one or more letters. (D.I. 146 at 11).

Examining the claim language and specification in light of the parties' arguments, the Court believes it is evident that there is a correlation between frame timing and frame alignment word. Indeed, based on FORE's argument, it appears that FORE agrees that the frame timing information has to do with alignment. Thus, as FORE contends, the question is whether the frame timing information must be more than one bit. The Court is not persuaded by FORE's argument that a "word" contemplates one or more bits just as "word" in the English language contemplates one or more letters. (D.I. 146 at 11). In the IEEE Standard Dictionary of Electrical and Electronic Terms, 6th Edition, there are sixteen different definitions of "word," all of which require more than one bit. (D.I. 152, Exh. M at A143-44). Accordingly, the Court concludes that "frame timing information" means frame alignment information comprised of more than one bit.

## d. filling the empty payload fields in said frames with data in packetized format

[10] According to Bellcore, an "empty payload field" means "bits or time periods representing an absence of source data to be transmitted." (D.I. 144 at 11). Consistent with its definition of "empty payload field," Bellcore contends that "filling the empty payload fields" refers to outputting source data when it is available during a payload field interval. In support of its position, Bellcore directs the Court to Figure 12 of the '306

Patent and that portion of the specification which provides: " *if the particular DTDM frame is empty and data is available* at the parallel input, a signal is applied by the control to the tristate device to enable the data to be inserted into the particular DTDM frame via bus before it leaves the framer unit." ('306 Patent, col. 16, lines 49-55 (emphasis added)).

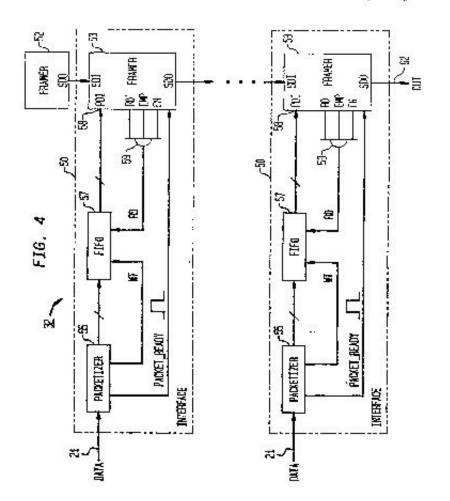

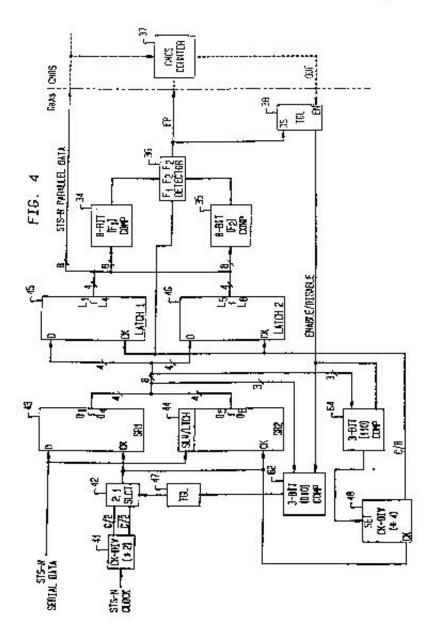

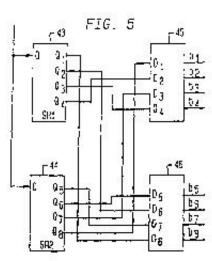

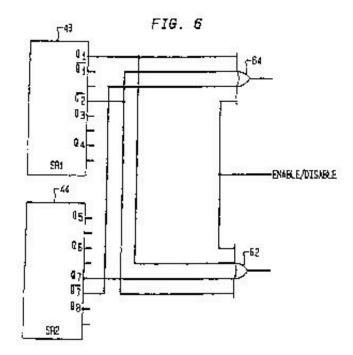

In response to Bellcore's proposed construction, FORE contends that an "empty payload field" means that a frame's payload has zero data in it. (D.I. 144 at 12). Consistent with its proposed construction of the term "empty payload field," FORE contends that "filling the empty payload fields in said frames" requires two steps: (1) that a complete empty frame is first created; and (2) after creation of the empty frame, the frame's payload is 100% filled with a packet. FORE contends that its construction is supported by the plain and ordinary meaning of the words used in the claim, as well as by the specification and prosecution history of the '306 Patent. For example, FORE points out that the language of Claim 1 contemplates generating multiple empty frames with frame timing information that can subsequently be filled with packets. FN2 FORE also points out that Figure 2 of the '306 Patent shows a generated train of empty frames entering the DTDM assembler. In addition, the language accompanying Figure 2 provides: "[A] train 10 of DTDM frames with empty payload fields is generated" and "[e]ach of the frames in the train 10 has an occupied transmission overhead field (T)." ('306 Patent, col. 7, lines 27-28). FORE further points out that Figure 4 and its accompanying text illustrates how the train of empty frames is generated in the first instance. The text provides: "The topmost framer 52 in Figure 4 does not have any input service connected to it. It generates the train of empty DTDM frames which are sent to the following framers 53." ('306 Patent, col. 9, line 59-61).

FN2. Fore relies on that portion of Claim 1 providing:

generating a bit stream comprising a *sequence* of frame *s*, each of said frame *s* including ... frame timing information and an empty payload field, and filling the empty payload field *s* in said frame *s* with data in packetized format....

('306 Patent, col. 17, lines 47-52 (emphasis added)).

In addition to the claim language and specification, FORE also directs the Court to the prosecution history of the '306 Patent. FORE contends that Bellcore distinguished prior art known as the Baran patent by stressing that the '306 Patent requires the generation of a sequence of empty frames first, and then filling the frames. Distinguishing Baran during the prosecution of the '306 Patent, Bellcore explained:

[T]he transmission bit streams are formed entirely differently in the claimed invention in Baran et al. Thus, as indicated above, the transmission stream of the claimed invention is formed by *first* generating a bit stream comprised of *frames with empty payload fields*. Data from a plurality of sources which have access to the transmission stream are packetized. The packets are *then* inserted into *the empty payload fields of the frames*. The Baran reference in no way discloses the formation of a transmission bit stream by generating a *sequence* of frame *s* with empty payload field *s* and picking up packets from a plurality of sources to fill the payload field *s*.

(D.I. 147, Ex. 7 at FSI001338 (emphasis added)). Similarly, Bellcore explained the '306 Patent during the prosecution with the following analogy:

The stream of empty frames may be analogized to a train of empty freight cars. The empty freight cars are filled with data in packetized format from various sources which have access to the train of freight cars. The

train, with its now filled freight cars, transmits the data to remote locations.

#### (D.I. 147, Ex. 7 at FSI001333 (emphasis added)).

After reviewing the parties' arguments in the context of the claim language, specification and prosecution history of the '306 Patent, the Court agrees with FORE's construction of the phrase "filling the empty payload fields in said frames with data in packetized format." The grammatical structure of the claim language confirms that multiple empty payload fields are generated, and then the empty payload fields are detected and then filled with packets. Stated another way, the frames cannot be filled until after they are generated and empty frames are detected. Indeed, the Court believes that this interpretation is consistent with Figures 2 and 4 of the patent specification and consistent with the position stressed by Bellcore during the prosecution of the '306 Patent. Accordingly, the Court construes the term "empty payload fields" to mean that a frame's payload has zero data in it. The Court further construes "filling the empty payload fields" to mean that first the empty frames must be generated, and second the frames' empty payloads are filled with data.

## e. data in packetized format from any of said sources is written into any available empty payload field of any of said frames

[11] In disputing the meaning of this phrase, Bellcore contends that this phrase means that packetized data can be placed into the payload field of any frame interval whenever a complete data packet becomes available. To this effect, Bellcore contends that the circuit does not wait for a particular frame or predetermined time to output the packet. Bellcore relies on Figures 4 and 12 of the '306 Patent in support of its argument. (D.I. 142 at 29).

In response to Bellcore's interpretation, FORE contends that this language means that packets are only put in frames that have zero data in their payload. FORE directs the Court to the "Summary of the Invention" section of the specification, which provides:

Illustratively, a DTDM multiplexer may be used to merge traffic from three different communications sources or tributaries into a single DTDM bit stream.... The available frames are shared by the three tributaries by giving higher priority to the circuit tributary, and allowing the voice and graphics tributaries to contend on a first-come, first-served basis. The circuit tributary *seizes one out of every three empty frames passing by* .... In this case the voice tributary will on average seize one out of every 2,160 frames. Similarly, at a rate of 1 Megabit per second, the graphics tributary will fill one frame out of 150. In this way, three diverse data streams are multiplexed into a single bit stream.

('306 Patent, col. 5, lines 13-38 (emphasis added)). According to FORE, this description of the invention makes it clear that each source detects and then "seizes" empty frames. FORE contends that once a packet is inserted into a frame, it is no longer empty so other sources will not seize the filled frame. Rather, if another source has a packet to send, it will insert its packet into the next "available empty frame."

The Court agrees with FORE's proposed construction. Indeed, this construction is consistent with the Court's conclusion that an empty payload field has zero data in it. In addition, the Court believes this interpretation is consistent with the description of the invention contained in the "Summary of the Invention" section of the specification of the '306 Patent. In the Court's view accepting Bellcore's proposed construction of this phrase would read the word "empty" out of the claim language. In Bellcore's own words its construction

would allow "any packet to be written into any frame." (D.I. 142 at 29). This construction is at odds with the claim's express language which requires the data to be written into "any *available empty payload field* of any of said frames." Accordingly, the Court concludes that the phrase "data in packetized format from any of said sources is written into any available empty payload field of any of said frames" means that packets are only put in frames which are empty, i.e. which have zero data in their payloads.

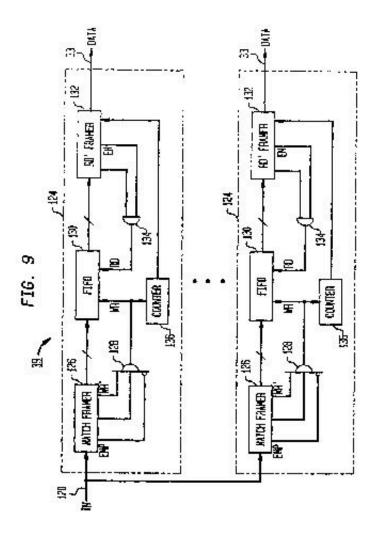

## f. for transmitting data from each of said sources at its own desired bit rate via said bit stream and for transmitting data from said plurality of sources simultaneously via said bit stream

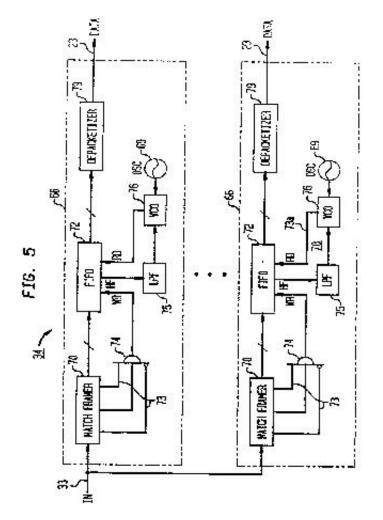

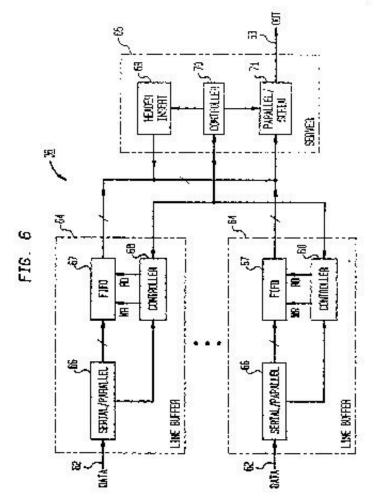

[12] Bellcore contends that this phrase means that the original bit rate of the sources is maintained for transmission of the source data in a bit stream emanating from a single transmitting device by multiplexing the packetized data within the transmitting device into frames as necessary. According to Bellcore, this means that the number of packets per second generated by a given source will equal the number of packets per second generated by a given source will equal the number of packets per second inserted into the output stream for that source. Bellcore relies on the specification of the '306 Patent for its construction, particularly emphasizing Figure 4. According to Bellcore, data from a source enters each interface 50 on data line 21. The data is packetized and stored in FIFO memory 57. The FIFO memories present the packets to the framers 53 in the order and at the rate that the packets are generated. Bellcore contends that the source data is transmitted simultaneously because it is "multiplexed," meaning the packets are interspersed into a common stream. In explaining its construction, Bellcore relierates that the claimed generating and filling steps are not limited to any particular sequential order. (D.I. 142 at 30).

In response to Bellcore's argument, FORE contends that Bellcore's proposed definition is wrong, because it does not follow that "the source data is transmitted simultaneously because it is 'multiplexed.' " (D.I. 153 at 9-10). FORE also contends that the '306 Patent describes several "multiplexors" which are different that the DTDM assembler of Figure 4, which is the subject of Claim 1 of the '306 Patent. Thus, FORE contends that the use of the word "multiplexed" would be confusing in this context.

In proposing an alternate construction of this phrase, FORE contends that this language means that "two or more empty frames are filled at the same time by different data sources." (D.I. 146 at 15; D.I. 153 at 9-10). According to FORE, the interface unit of each source has access to the bit stream at the same time, so that the interface unit of each source can insert packets into passing empty frames at the same time. According to FORE, simultaneous transmission from multiple sources requires that each source have its own insertion point into the bits stream, otherwise the sources would not be transmitting simultaneously.

The Court agrees with FORE's construction of this phrase. In the Court's view, this construction is supported by both the plain meaning of the word "simultaneously" as used in the claim and by the specification of the '306 Patent. ('306 Patent, col. 13, lines 49-51). Accordingly, the Court construes the phrase "for transmitting data from each of said sources at its own desired bit rate via said bit stream and for transmitting data from said plurality of sources simultaneously via said bit stream" to require two or more empty frames to be filled at the same time by different data sources.

## 2. Claim 3 of the '306 Patent

In full, Claim 3 of the '306 Patent provides:

A method for generating a bit stream capable of transporting data originating from both circuit transmission and packet sources comprising

generating a bit stream comprising a sequence of frames, each of said frames including a transmission overhead field containing frame timing information and an empty payload field,

packetizing data from a plurality of sources having different bit rates and which have access to said bit stream including circuit transmission sources or customer premises equipment to produce data packets, and

inserting said packets from said sources into the empty payload fields of frames such that a packet from any of said sources is inserted into any available empty payload field of any said frames for transmitting data from each of said sources at its own desired bit rate via said bit stream and for transmitting data from said plurality of sources simultaneously using said bit stream.

The Court will examine each of the disputed terms and phrases below.

#### a. generating a bit stream

For the reasons discussed previously, the Court concludes that this phrase has the same meaning as described in the Court's analysis of this language in Claim 1.

#### **b.** frame timing information

For the reasons discussed previously, the Court concludes that this phrase also has the same meaning as described in the Court's analysis of this language in Claim 1.

#### c. an empty payload field

For the reasons discussed previously, the Court concludes that this phrase has the same meaning as described in the Court's analysis of this language in Claim 1.

#### d. inserting said packets from said sources into the empty payload fields of said frames

The parties' dispute concerning this language is essentially the same dispute raised in the context of the "filling the empty payload fields" language of Claim 1. Consistent with its argument related to the "filling" language in Claim 1, Bellcore contends that "inserting said packets from said sources into the empty payload fields of said frames" refers to outputting source data packets when available during a payload field interval. Consistent with its previous argument, FORE contends that the inserting step cannot occur until the empty frames have been generated. For the reasons discussed previously, the Court agrees with FORE and construes this language in the same fashion as the "filling" language in Claim 1.

## e. such that a packet from any of said sources is inserted into any available empty payload field of any of said frames

For the reasons discussed previously, the Court construes this phrase in accordance with the construction provided by the Court in its analysis of the similar language FN3 used in Claim 1.

FN3. The language used in Claim 1 is virtually identical to this language except that Claim 1 reads "data in packetized format" instead of "a packet" and "written into" instead of "inserted into."

## f. for transmitting data from each of said sources at its own desired bit rate via said bit stream and for transmitting data from said plurality of sources simultaneously using said bit stream

The parties' arguments regarding the construction of this phrase are premised on their arguments relating to the comparable language in Claim 1. Accordingly, for the reasons discussed previously, the Court will construe this phrase in accordance with the construction provided by the Court in its analysis of the comparable language used in Claim 1.

## 3. Claim 4 of the '306 Patent

In full, Claim 4 of the '306 Patent provides:

An apparatus for assembling a dynamic time division multiplexing bit stream comprising,

generating means for generating a train of frames wherein each frame includes a transmission overhead field containing timing information and an empty payload field,

processing means for processing data from a plurality of sources into packet format, and

inserting means for receiving said train of frames and for inserting each of said packets comprised of data from one of said plurality of sources into any empty payload field of any of said frames available to said inserting means to form said bit stream so that data from each of said sources can be transmitted at its own desired bit rate via said bit stream and so that data from said plurality of sources can be transmitted simultaneously via said bit stream.

[13] Although Claim 4 contains many of the same limitations included in Claim 1, the parties agree that Claim 4 is an apparatus claim which recites many limitations in a "means-plus-function" format. Means-plus function elements must be interpreted under 35 U.S.C. s. 112, para. 6. In pertinent part, Section 112, para. 6 provides:

An element in a claim for a combination may be expressed as a means or step for performing a specified function without the recital of structure, material, or acts in support thereof, and such claims shall be construed to cover the corresponding structure, material, or acts described in the specification and equivalents thereto.

Although use of means-plus-function language in a claim is permissible, a means clause does not encompass every means for performing the specified function. *The* Laitram Corporation v. Rexnord, 939 F.2d 1533, 1535 (Fed.Cir.1991). Rather, the limitation must be construed "to cover the corresponding structure, material, or acts described in the specification and equivalents thereof." Odetics, Inc. v. Storage Technology Corp., 185 F.3d 1259, 1999 WL 455530, (Fed.Cir. July 6, 1999).

With these principles in mind, the Court will examine each of the disputed terms and phrases of Claim 4.

#### a. bit stream

In disputing the meaning of this term, Bellcore requests construction of more than the phrase "bit stream." Bellcore requests construction of the phrase "dynamic time division multiplexing bit stream." According to Bellcore, this phrase refers to a desired output transmission stream of bits that includes a sequence of transmission frames and dynamically multiplexed packets, i.e. packets multiplexed into the assembled bit stream at the rate they are generated.

FORE does not proffer a definition for the entire phrase "dynamic time division multiplexing bit stream," but merely contends that bit stream means the same as its proffered definition for the phrase "generating a bit stream" in Claim 1.

For the reasons discussed previously, the Court rejects FORE's definition of a bit stream as being limited to a serial configuration of bits. However, because FORE does not address Bellcore's argument or the language "dynamic time division multiplexing," it is unclear to the Court whether FORE agrees or disputes Bellcore's construction of this term. Accordingly, the Court will reserve decision on the meaning of this phrase until such time as the parties' clarify their respective positions.

## **b.** generating means for generating a train of frames wherein each frame includes a transmission overhead field containing frame timing information and an empty payload field

[14] The parties agree that this claim element is recited as a means-plus-function element. Bellcore contends that the disclosed structure corresponding to the "generating means" includes control 210, tristate device 222, ROM 224 and timing generator 209. Bellcore contends that these are the only structural elements shown in the specification which are involved in performing the claimed function of generating empty frames, and therefore Bellcore contends that it is improper to identify the entire framer as the structure corresponding to the generating means.

FORE contends that the structure of the generating means is the entire framer unit shown in Figure 12 and described in the specification. ('306 Patent, col. 16, line 8-col. 17, line 30). In response to Bellcore's reliance on only a portion of the framer unit, FORE contends that Bellcore provides "no analysis that some subset of the structure could even work without all of the components on that page." (D.I. 153 at 11). To this effect, FORE points out that the specification acknowledges the framer unit as an "important component" of the process. ('306 Patent, col. 15, lines 8-11).

The Court agrees with Bellcore. Although the specification repeatedly explains that the framer unit generates trains of empty frames, the specification also expressly identifies those structures of the framer unit involved in the generating means as control 210, tristate device 222, ROM 224 and timing generator 209. ('306 Patent, col. 16, lines 27-31; col 16, lines 62-col. 17, line 7). That the entire framer unit is not involved in the process is further confirmed by the specification which expressly provides that "the serial input 202 and *associated serial-to-parallel converter 212 are not utilized.*" ('306 Patent, col. 16, lines 64-65 (emphasis added)). Accordingly, the Court concludes that the structures corresponding to the "generating means" are control 210, tristate device 222, ROM 224 and timing generator 209.

#### c. processing means for processing data from a plurality of sources into packet format

[15] The parties' agree that this element is asserted in a means-plus-function format. However, Bellcore contends that the disclosed structure corresponding to this language includes packetizers 55 and their equivalents. Bellcore contends that this does not include the FIFOs because the FIFOs store packets after they have been formed and are not involved in packetizing.

FORE contends that the disclosed structures corresponding to this language are both the packetizers 55 and the FIFOs. Although FORE contends that it is essential for each source to have its own packetizer and FIFO,

FORE's argument focuses on the reason for including the packetizer and not on its reason for including the FIFO.

The Court agrees with Bellcore that the structures indicated in the specification for performing this function are the packetizers 55 and not the FIFO memories. As the specification states, "packetizer 55 puts the incoming data into a packet structure" and it is only "*after* the data is put into a packet structure" by the packetizers 55, that the data "is stored in a FIFO 57." ('306 Patent, col. 9, lines 19-21, 28-30 (emphasis added)). Accordingly, the Court concludes that the packetizers 55 are the structures which perform the function recited in this element.

#### d. inserting means for receiving said train of frames and for inserting each of said packets comprised of data from one of said plurality of sources into any empty payload field of any of said frames available to said inserting means to form said bit stream so that data from each of said sources can be transmitted at its own desired bit rate via said bit stream and so that data from said plurality of sources can be transmitted simultaneously via said bit stream

[16] As with the prior elements, the parties agree that this element is recited in a means-plus-function format. Bellcore contends that the structures corresponding to the "inserting means" include control 210, tristate device 218, tristate device 220, frame detect 214 and timing generator 209.

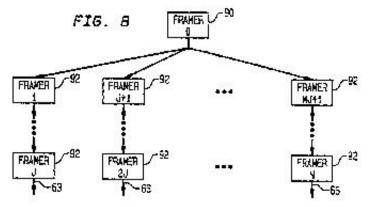

In contrast to Bellcore's designations, FORE contends that the inserting means is multiple framer units arranged in a daisy chain. FORE directs the Court to Figure 4 which depicts a daisy chained configuration of framer units inserting packets into an empty train of frames and to Figure 12 and its accompanying text which describes how the framer 200 writes packet data into empty frames. ('306 Patent, col. 16, lines 32-61).

The Court agrees with Bellcore. The specification of the '306 Patent explains the inserting means in detail. ('306 Patent, col. 16, lines 39-58). According to the specification, the timing information for the framer unit is provided by timing generator 209. The DTDM frame is converted to parallel form and is detected by frame detector 214. The frame detector 214 is in communication with the control 210 which detects whether the frame is empty. The frame cannot reach the parallel to serial converted unless the control 210 applies a signal to the tristate device 218. If the frame is empty, a signal is applied by the control 210 to the tristate device 220 to enable the data to be inserted into the particular frame. ('306 Patent, col. 16, lines 43-58).

With regard to FORE's position that the structural means is multiple framer units arranged in a daisy chain, the Court acknowledges that the specification indicates that the "framer units *may* be connected in a daisy chain fashion." ('306 Patent, col. 16, lines 32-33 (emphasis added)). However, a daisy chain configuration is not a mandatory requirement. Further, as indicated above, the specification precisely outlines those structures which are involved in the insertion means. Accordingly, the Court concludes that the structures corresponding to the "inserting means" are control 210, tristate device 218, tristate device 220, frame detect 214 and timing generator 209.

## B. The '768 Patent

Bellcore asserts Claims 13 of the '768 Patent. In full, Claim 13 reads:

The method for demultiplexing a serial data bit stream consisting of a continuum of an interleaved multiplicity of data bytes of predetermined size derived from a plurality of identically-formatted

contributory frames each containing a plurality of said data bytes, and for reconstructing said data bytes and identifying from among them a benchmark from which may be determined the beginning byte of each of such contributory frames and, thereby, the boundaries of such frames, said method comprising:

(a) accumulating data bits from said serial stream to form bytes having the same predetermined number of bits as do said interleaved data bytes;

(b) comparing at least one bit pattern from each byte thus formed with at least one bit pattern known to have comprised a byte of each of said contributory frames;

(c) providing a first signal when a match is detected between said compared patterns;

(d) effecting in response to said first signal the output of the byte of matching bit pattern, and each byte thereafter formed of newly accumulated bits, as said reconstructed bytes;

(e) comparing bit patterns from a contiguous plurality of said output reconstructed bytes with bit patterns known to have comprised a like contiguous plurality of bytes of each of said contributory frames;

(f) providing a second signal as said benchmark identification when a match is detected between said compared patterns; and

(g) effecting in response to said second signal discontinuation of the provision of said first signal.

The Court will examine each of the disputed terms and phrases below.

# **1.** demultiplexing a serial data bit stream consisting of a continuum of an interleaved multiplicity of data bytes of predetermined size derived from a plurality of identically-formatted contributory frames each containing a plurality of said data bytes

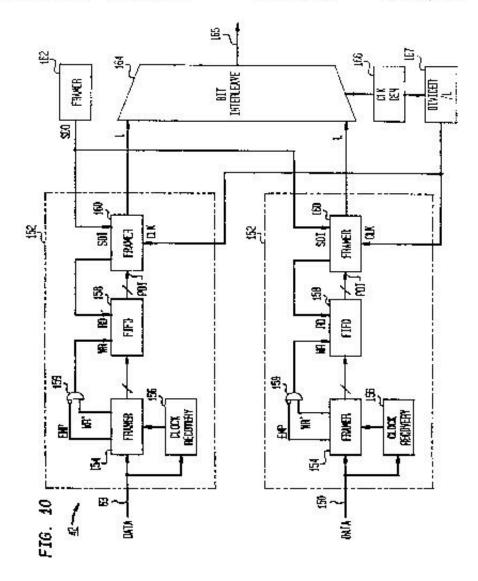

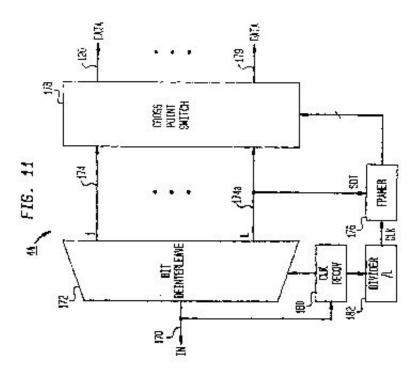

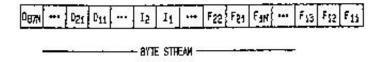

[17] According to Bellcore, the phrase "demultiplexing a serial data bit stream" means detecting the bits in the serial bit stream and converting them to a sequence of byte groupings. (D.I. 142 at 38; D.I. 144 at 3). Bellcore contends that the term "demultiplexing" is not defined in the '768 Patent, but that one skilled in the art would understand that bit streams are "demultiplexed" or converted to a sequence of data bytes representing the bytes of the original frame. Relying on the specification, Bellcore explains that "[i]n the general application of the present invention, the high-speed serial bit stream of the STS-N level, e.g. STS-24 transmission is demultiplexed to the basic SONET 8-bit byte-parallel format..." ('768 Patent, col. 3, lines 8-11). The SONET frames "are transmitted in the continuing serial bit stream to their destined terminating SONET receiver where the frames must be reformatted by reconstructing and demultiplexing the transmitted bytes in order and sequence." ('768 Patent, col. 4, lines 22-27). According to Bellcore, the specification further explains that the invention "provides for the maximum utilization of available technologies for optimum economies of power and time in the demultiplexing of high speed serial bit data transmission to low-speed byte-parallel format within the SONET signal hierarchy." ('768 Patent, col. 9, lines 49-54).

Bellcore further defines the phrase "consisting of a continuum of an interleaved multiplicity of data bytes of predetermined size derived from a plurality of identically-formatted contributory frames each containing a plurality of said data bytes" to mean that the serial bit stream consists of transmitted SONET-like frames greater than STS-1. In proffering this definition, Bellcore specifically defines "a continuum of an

interleaved multiplicity of data bytes of predetermined size" as a sequence of interspersed bytes, usually eight bits in size, but not required to be eight bits in size. Bellcore also defines "derived from a plurality of identically-formatted contributory frames each containing a plurality of said data bytes" as the format of the sequence of interspersed bytes. Specifically, Bellcore contends that this phrase means having a format based on multiple basic frames having the same byte format.

In contrast to Bellcore's interpretation, FORE contends that the preamble requires each frame of the serial bit stream that is being demultiplexed to have been formed by interleaving all eight bit bytes of two or more contributory frames. (D.I. 146 at 25). In other words, FORE's definition focuses on how the serial bit stream referred to in the claim was formed. According to FORE, the serial bit stream consists of a train of repeating higher-level frames. Each higher level frame is constructed by combining two or more pre-existing, distinct and complete lower-level frames called "contributory frames." FORE further contends that this language means that there can be no gaps or pauses or breaks in the interleaving of the contributory frames. In support of its position, FORE contends that the specification makes clear that demultiplexing is the process of disassembling previously multiplexed (or combined) lower-level SONET frames. ('768 Patent, col. 1, lines 37-44; col. 2, lines 28-30; col. 5, lines 41-47). Stated another way, FORE contends that "demultiplexing" is the process of separating higher-level, higher speed STS-N frames transmitted in the serial data bit stream into the lower-level, lower speed STS-1 frames that make up each STS-N frame. Thus, according to FORE, the claim is limited to taking multiplexed STS-N frames.

In addition, FORE specifically disputes Bellcore's construction of the words "continuum," "interleaved" and "byte." FORE contends that the word "continuum" means "continuous" and not "a sequence" as Bellcore contends. As for Bellcore's interpretation of the words "interleaved" and "byte," FORE contends that Bellcore's definitions are overly-broad, and therefore, inconsistent with the patent's specification.

The Court agrees with FORE that the preamble limits this claim of the patent to taking multiplexed STS-N frames and separating them into the original STS-1 frames that were previously combined to create the STS-N frames. The specification of the '768 Patent speaks solely in terms of multiple, lower-speed frames that are multiplexed together to form a higher speed frame. The patent does not address the type of SONET framing structure which consists of larger frame formats generated in a single operation, using the higher bit rate and multiple STS-1 frame format. In order for the invention to perform its demultiplexing function, the bit stream must be multiplexed. The specification of the '768 patent expressly defines a multiplexed bit stream as follows: "[A] multiplexed serial bit stream is assembled by interleaving repeated sequential extractions of one byte from each of the component STS-1 frames." ('768 Patent, col. 1, lines 37-40). The patent specification further provides:

It is *necessary*, therefore, that the signal receiver [the device receiving the SONET-formatted serial bit stream] *reconstruct* from this serial bit stream *the original base frame*, or some frame multiple thereof, in order that the correct substance of the transmitted signal may be recovered.

\* \* \* \* \* \*

[The] stream must be reformatted into the *original bytes and frames* in order for the receiver processing circuitry to property extract the transmitted data and messages.

('768 Patent, col. 1, lines 37-44 (emphasis added); col. 2, lines 28-30 (emphasis added)). Further, the

specification explains:

Upon completion of the formatting of the high-speed input serial data stream to a low-speed, properly synchronized byte-parallel data stream, there remains the problem of identifying the boundaries of *each frame of the original transmission* in order that the payload, as well as the relevant overhead information bytes, may be *demultiplexed to the basic STS-1 level*.

('768 Patent, col. 5, lines 41-47 (emphasis added)). Accordingly, based on the claim language and the specification, the Court concludes that the phrase "demultiplexing a bit stream" refers to taking multiplexed STS-N frames and separating them into the original STS-1 frames that were previously combined to create the STS-N frames.

[18] The Court further agrees with FORE that the serial bit stream that is being demultiplexed must have been formed by interleaving the bytes of two or more contributory frames, that each of the contributory frames must have exactly the same format, and that there can be no gaps or pauses in the interleaving. In the Court's view, the specification and Figure 2 support FORE's position that the bytes are continuously interleaved from each of the contributory frames. ('768 Patent, col. 1, lines 37-40; col. 4, lines 9-27). Indeed, byte-interleaving is described in the specification as requiring a byte to be taken, one at a time, from the same byte position of each contributory frame and placed in the bit stream. ('768 Patent, col. 4, lines 9-27). However, the Court cannot accept FORE's contention that a byte is limited to 8 bits. Although Bellcore concedes that a byte is usually 8 bits, the Court cannot conclude that the patent limits a byte to 8 bits, because the express language of the claim indicates that the data bytes are of a "predetermined size." If bytes were limited to 8 bits only, then the language "predetermined size" would be superfluous and unnecessary. Each and every word in a claim must have meaning and cannot be ignored. *See e.g.* Exxon Chem. Patents, Inc. v. Lubrizol Corp., 64 F.3d 1553, 1557 (Fed.Cir.1995). Accordingly, in order to give effect to the language "predetermined size" the Court will not exclude the possibility that a byte could be more than 8 bits.

As to the parties' dispute concerning the phrase "consisting of," the Court concludes that in this case, the phrase "consisting of" is used as a transition between the claim element "a serial data bit stream" and the clause that follows and modifies the claim element. Because the phrase "consisting of" introduces the modifying clause, "a continuum of an interleaved multiplicity of data bytes of a predetermined size derived from a plurality of identically-formatted contributory frames each containing a plurality of said data bytes," the Court concludes that it excludes any bit stream that does not have the exact limitations recited in the modifying clause. Georgia-Pacific Corp. v. U.S. Gypsum Co., 195 F.3d 1322, 1327 (Fed.Cir.1999); Mannesmann Demag Corp. v. Engineered Metal Prods. Co., 793 F.2d 1279, 1282 (Fed.Cir.1986).

In sum, the Court concludes that the phrase: "The method for demultiplexing a serial data bit stream consisting of a continuum of an interleaved multiplicity of data bytes of predetermined size derived from a plurality of identically-formatted contributory frames" means that each frame of the serial bit stream that is being demultiplexed was formed by interleaving the bytes of two or more contributory frames. Each contributory frame must have exactly the same format and there can be no gaps or pauses in the interleaving.

## 2. reconstructing said data bytes; said reconstructed data bytes

[19] In interpreting this phrase, FORE contends that "reconstructed bytes" are bytes from the contributory

frames that have been aligned, latched, and converted from serial to parallel format. Bellcore contends that the phrase means "identifying the byte groupings of the transmitted frame." (D.I. 151 at 14). However, Bellcore further contends that it essentially agrees with Fore's proposed construction, but that it is inappropriate to include the "latched" limitation in step (d) where the word "reconstructed bytes" appears.

The Court disagrees with Bellcore. The specification describes the process of reconstructing bytes as aligning, latching and converting the bytes from serial to parallel format. Detecting the first frame byte F1 by comparing bits in the incoming serial stream to the known bit pattern "trigger[s] the output of the matched F1 framing byte and begin[s] clocking *reconstructed*, *properly-phased 8 bit bytes out of latch 33* ..." Patent, col. 5, lines 31-36 (emphasis added). Thus, as the specification indicates, latching is part of the reconstruction process, and reconstruction is not simply identifying byte groupings, as Bellcore contends. Accordingly, the Court concludes that "reconstructed bytes" or "reconstructing said data bytes" refers to bytes that have been aligned, latched and converted from serial to parallel format.

## **3.** identifying from among them a benchmark from which may be determined the beginning of each of such contributory frames and, thereby, the boundaries of such frames

[20] In disputing the meaning of this phrase, Bellcore contends that the term "benchmark" means marker and the term "boundaries" means the beginnings or ends of certain portions of a frame. Bellcore contends that the transition from F1 to F2 framing bytes serves as the "benchmark." (D.I. 252 at 15).

FORE contends that this limitation means that (1) a benchmark must be determined for each instance of higher-level frames, (2) from the benchmark the first byte of each distinct and complete higher-level frame must be determined, and (3) from that first byte, the boundary of each distinct and complete higher-level contributory frame must be determined. (D.I. 253 at 3-4). FORE does not appear to disagree with Bellcore's definition of "benchmark." Additionally, FORE agrees that the term "boundaries" means the beginning or end of a frame, but disagrees to the extent that Bellcore construes this term to mean "certain other portions" of a frame, which FORE contends is vague.

It appears to the Court that the parties central disagreement concerning the meaning of this phrase is whether the frame boundaries "must" be determined as FORE contends or "may" be determined as Bellcore contends. Reading the claim language as a whole in light of the specification, the Court agrees with FORE that this element requires the beginning of each frame, and therefore the frame boundaries, to be determined from the benchmark. As the specification states, "[I]t is essential to the proper recovery of the original SONET frames that the byte assembly be correctly synchronized and the boundaries of each frame be identified in the bit stream transmission in order that the reconstructed bytes will duplicate each of the bytes which were interleaved to produce that serial transmission signal." ('768 Patent, col. 1, lines 47-53 (emphasis added)). In the Court's view, accepting Bellcore's contention renders the requirement of identifying the benchmark a useless exercise. The very purpose of identifying the benchmark is to determine the "beginning byte" and the "boundary" of each contributory frame, and therefore, the Court cannot accept a construction of the phrase "may be" which would make this function optional. Accordingly, the Court concludes that this phrase requires that (1) a benchmark must be determined for each instance of higherlevel frames, (2) from the benchmark the first byte of each distinct and complete higher-level frame must be determined, and (3) from that first byte, the boundary of each distinct and complete higher-level contributory frame must be determined.

#### 4. comparing bit patterns from a contiguous plurality of said output reconstructed bytes with bit

#### patterns known to have comprised a like plurality of bytes of each of said contributory frames

[21] FORE contends that this phrase requires "bit patterns from two or more *adjacent* reconstructed bytes to be compared with bit patterns known to have been present in two or more *adjacent* bytes in *each* of the contributory frames which have been multiplexed to form the bit stream." (D.I. 146 at 31 (emphasis in original)). FORE further contends that each contributory frame must both contain the pattern and contain it within two or more adjacent bytes of the contributory frame.

In response to FORE's construction, Bellcore contends that this phrase means "that the contributory frames each have a plurality of bytes like the bytes included in the compared 'contiguous plurality' of bytes." (D.I. 151 at 16). According to Bellcore, this phrase cannot mean, as FORE contends, that the compared contiguous plurality must exist within each contributory frame. According to Bellcore, the requirement for byte interleaving makes this arrangement impossible.

The Court agrees with FORE's construction of this phrase. This element of the patent concerns frame boundary detection *after* byte reconstruction, because as the claim recites, the comparison is made from a "contiguous plurality of output *reconstructed* bytes." ('768 Patent, col. 12, line 12). Because this step is performed after the interleaved bytes are reconstructed, Bellcore's contention that the interleaving arrangement makes this interpretation impossible is incorrect. As the specification states:

*Upon completion* of the formatting of the high-speed serial data stream to a low-speed, *properly synchronized* byte-parallel data stream, there remains the problem of identifying the *boundaries of each frame* of the original transmission in order that the payload, as well as the relevant overhead information bytes, may be demultiplexed to the basis STS-1 level. For this purpose, the present invention relies upon the prescribed bit sequence of both the F1 and F2 framing bytes, of which each frame above STS-1 will have at least two, F2 bytes following immediately upon the final F1 framing byte as depicted in FIG. 2.

('768 Patent, col. 5, lines 41-52 (emphasis added)). The reference to Figure 2 here is only for the purpose of illustrating that the F2 bytes follow the F1 bytes. Accordingly, the Court concludes that "comparing bit patterns from a contiguous plurality of said output reconstructed bytes with bit patterns known to have comprised a like contiguous plurality of bytes of each of said contributory frames" means that two or more adjacent reconstructed bytes are compared with bit patterns known to have been present in two or more adjacent bytes in each of the contributory frames which have been multiplexed to form the bit stream. Each contributory frame must contain the bit pattern and each frame must contain the bit pattern within two or more adjacent bytes of the contributory frame.

## CONCLUSION

For the reasons discussed, the Court has construed the disputed terms of the '306 and '768 as provided herein. An Order consistent with this Opinion will be entered setting forth the meaning of the disputed terms in the '306 and '768 Patents.

## ATTACHMENT

#### ATTACHMENT

#### United States Patent 119.

#### Chao et al.

- [34] METHOD AND APPARATUS FOR MULTIPLEXING CIRCUIT AND PACKET TRAFFIC

- [75] INVESTOR. Hung-Hainng J. Chan, Madjaon; Sang. H. Lee, Bridgewater; Liang T. Wu, Gladstone, aB of N.J.

- [73] Assigned: Bell Complementations Research, Inc., Livingston, N.J.

- [21] Appl. No.: 119,977

- (22) Filed: Nov. 10, 1987

- 370/112, 112, 82, 110.1, 89 (56) References Cited

#### U.S. PATENT DOCUMENTS

| 4,321,701 | 2/1982  | Schwilerer et al      |

|-----------|---------|-----------------------|

| 4,516,240 | 5/1985  | Kume et al            |

| 4,594,708 | 6/1986  | Servel et al          |

| 4,683.105 | 8/1987  | Shikame et al         |

| 4,700,246 | 11/1987 | Xome                  |

| 4,763,3[9 | \$/1985 | Rotenblit             |

| 4,764,921 | 8/1983  | Graves et al          |

| 4,775,425 | 9/1988  | Baran et al 370/110.1 |

|           |         |                       |

#### OTHER PUBLICATIONS

R. W. Mulse, et al., "Experiments in Widehand Packet.

| $\{11\}$ | Patent Number: | 4,893,306 |

|----------|----------------|-----------|

|          |                |           |

#### (45) Date of Patent: Jan, 9, 1990

Technology", Proc. 1986, 3(teruntional Zurie), Seminar on Digital Communications, pp. 126-138.

W. W. Chu, "A Study of Asymptotomus Time Division Multiplexing for Time Shating Computer Systems", Proc. APTPS, vol. 35, pp. 669-678, 1969.

A. Thomas, et al., "Asynchrouods Time Division Trabniques: An Emperimental Packet Network Integrating Visco Communication", Proc. International Switching Symposium, May 1984.

Plinary Examiner-Douglas W. Olans Assistant Examiner-Min Jung

Attorney, Agent, or Firm-James W. Falk

#### [57] ABSTRACT

A data transmission technique referred to herein as Dynamic Time Division Multiplexing (15712)M) is disclosed along with a set of multiplexers and demultiplexers required to apply DTDM in all solual telecommunications network. The DTDM technique uses a transmission format which is compatible with the existing digital circuit transmission format and the packet transmission format so that DTDM is able to handle the transmission of elsenit and packet traffic. Thus, DTDM provides a flavible migration mustery between present circuit actworks and future broadband packet networks.

#### 7 Chairms, 10 Drawing Sheets

\*657

FIG. 3

FIG. 4

**FIG. 5**

FIG. 6

**FIG. 7**

FIG. 8 FIG. 9

FIG. 10

FIG. 11

FIG. 12

FIG. 13

## ĭ

#### METHOD AND APPARATUS FOR MULTIPLEXING CIRCUIT AND PACKET TRAFFIC

#### RELATED APPLICATIONS

"(be following applications contain subject matter related to the subject matter of the present application, are assigned to the assignee hereof and have been filed on the stand date as the present application.

- J. J. Chao, "DTDM Multipleter With Cross-Point Switch", Ser. No. 118,979, now U.S. Pat. No. 4,855,999, Issued Aug. 8, 1989

- Souther, Ser. No. 148,975, inter Co.

A.S.S. 199, Issued Aug. 8, 1989

M. W. Beckmer, F. D. Porter, K. Shu, "DTDM Multiplexing Circulary", Ser. No. 118,897, now <sup>15</sup> U.S. Pat. No. 4,833,671, issued May 23, 1989

H. J. Chao, S. H. Lee, "Time Division Multiplexer for Division Science for March 110 Oct."

- H. J. Chao, S. H. Lee, "Time Division Multiplexer for DTDM Bit Streams", Ser. No. 113,978, now U.S. Pat. No. 4,833,673, issued May 23, 1989

- M. W. Beckner, J. J. Chao, T. J. Robe, L. S. Smoot, <sup>20</sup> "Framer Circuit", Ser. No. 118,898, now U.S. Pat-No. 4,819,226, issued Apr. 4, 1989.

#### FIELD OF THE INVENTION

This invention relates to the transmission of data in <sup>25</sup> telecommunications networks. More particularly, the present invention relates to a data transmission technique referred to hards as Dynamic Time Division Multiplexing (DTDM), and a set of multiplexers and demultiplexers required to apply DTDM in an actual 30 telecommunications network. DTDM is capable of effectively handling both circuit and packet traffic and thus provides a migration strategy between the present circuit switched telephone network. 35

#### BACKGROUND OF THE INVENTION

Presently, there are significant uncertainties when it comes to predicting the future demand for broadband. telecontributions services such as high definition 40 video and interactive data committationtions. This uncertainty in the future demand for broadband telecommunications services has a significant impact on the design of public telephone petworks. First, to satisfy the unknown growth pattern in future service domands, it is 45 desirable to have a robust actwork design that can be easily modified in response to changes in demand for particular telecommunications services. Second, the network must be able to handle vastly different types of traffic ranging from low speed data and voice to full 50 motion video. Third, depending on the demand for widebaad services, a network design must be canable of providing a migration scrategy from existing copper wires and orrenit transmission and switching facilities to optical fibers and the succeeding generations of high 55 speed packet transmission and twitching facilities, which packet facilities are used in connection with the delivery of wideband telecommunications tervices. These three criteria determine the selection of the three major components of a network design: network topol- 60 ogy, transmission systems and awitching systems. Here, the concern is primarily with transmission systems and transmission techniques which meet the foregoing critesla.

Two important types of commercially used transmis- 65 sion systems are circuit systems and packet systems. Typically, circuit systems utilize time division multiolexing (TDM) as a transmission technique. When

TDM is used, each data stream, comptyees frames which are subdivided into stots. Corresponding slots in each frame are allowated to specific connections. For example, the first slot in each frame is allocated to one spe-> cific connection and the second slut in each frame is allocated to a second connection, ste, Each frame sist includes a field which contains transmission overhead information including freme synchronization words and control words. This traditional circuit transmission for-10 mat can be extended to multiple but rate anyways by allocating multiple slots in each frame to high bandwidth services. In such circuit manufation systems, a combination of space division switching and time division switching is utilized at the network switches to swap time slots between various bit screams so that connections to and between specific subscribers are establiahed.

Historically, the first digital circuit transmission tystens were introduced during the 1960's. These first digital circuit transmission systems were introduced in later-office tranking applications to carry 24 voice cimanels by a single 1.544 Mb/see digital stream. This is known as the DS-1 signal. Subsequently, the wide deployment of digital channel banks in the public telephone network required the audiplexing of several DS-1 signals into a higher speed bit stream to efficiently utilize available transmission links. As the network grow further, continuing efforts to effectively multiplex tributaries having different bit tates into a countrat bit stream resulted in the well-known hierarchical matiplexing plan comprising the DS-1 (1.544 Mb/sec), DS-1C (3.152 Mb/sec), DS-2 (6.312 Molt/sec), DS-3 (44.736 Mb/sec) and DS4 274.176 Mb/sec signals.