United States District Court, E.D. Texas, Texarkana Division.

LG ELECTRONICS, INC, Plaintiff. v. HITACHI, LTD., et al, Defendants.

Civil Action No. 5:07-CV-90 (DF)

Dec. 8, 2008.

**Background:** Holder of patents relating to digital display systems brought action against competitor, alleging infringement.

Holdings: The District Court, Folsom, J., held that:

(1) terms relating to patent for automated flat-panel display control system would be construed, and (2) limitations relating to patent would be construed.

So ordered.

6,404,418. Cited.

Michael J. McKeon, Stephanie Deckter, Andrew C. Warnecke, Brian T. Racilla, James A. Fussell, III, Steven A. Bowers, Fish & Richardson, PC, Washington, DC, Geoffrey Patton Culbertson, Justin Kurt Truelove, Nicholas H. Patton, Patton Tidwell & Schroeder, LLP, Texarkana, TX, Patricia L. Peden, Law Offices of Patricia L. Peden, Emeryville, CA, Robert Lawrence Rickman, Fish & Richardson, Dallas, TX, for Plaintiff.

Craig D. Leavell, Howard E. Levin, Wengang He, William A. Streff, Jr., Kirkland & Ellis, LLP, Chicago, IL, Eric Hugh Findlay, Findlay Craft, Tyler, TX, for Defendants.

# CLAIM CONSTRUCTION ORDER (4 OF 4) REGARDING U.S. PATENT NO. 5,790,096

#### DAVID FOLSOM, District Judge.

#### Table of Contents

I. Introduction .....

| II. | U.S. | . Patent No. 5,790,096 |            |                            | 1                                                                |        |

|-----|------|------------------------|------------|----------------------------|------------------------------------------------------------------|--------|

|     | Α.   | Overview               |            |                            | 1                                                                |        |

|     |      | 1.                     | Bac        | kground                    |                                                                  | 1      |

|     |      | 2.                     | Disclosure |                            |                                                                  |        |

|     |      | 3.                     | The        | Asserted Cla               | ims                                                              | 4      |

|     | Β.   | Claim Construction     |            |                            | 5                                                                |        |

|     |      | 1.                     | Agr        | eed Terms                  |                                                                  | 5      |

|     |      | 2.                     | Dis        | puted Terms .              |                                                                  | 5      |

|     |      |                        | a)         | "orientation'              | '                                                                | 5      |

|     |      |                        |            | (1)                        | The Parties' Positions                                           | 5      |

|     |      |                        |            | (2)                        | Construction                                                     | 7      |

|     |      |                        | b)         | "video imag                | e"                                                               | 11     |

|     |      |                        |            | (1)                        | The Parties' Positions                                           | 12     |

|     |      |                        |            | (2)                        | Construction                                                     | 14     |

|     |      |                        | c)         | "video signa               | 1"                                                               | 19     |

|     |      |                        |            | (1)                        | The Parties' Positions                                           | 19     |

|     |      |                        |            | (2)                        | Construction                                                     | 21     |

|     |      |                        | d)         | "video signa               | l data rate"                                                     | 22     |

|     |      |                        |            | (1)                        | The Parties' Positions                                           | 23     |

|     |      |                        |            | (2)                        | Construction                                                     | 24     |

|     |      |                        | e)         | "flat panel d              | isplay"                                                          | 24     |

|     |      |                        |            | (1)                        | The Parties' Positions                                           | 25     |

|     |      |                        |            | (2)                        | Construction                                                     | 26     |

|     |      |                        | f)         | "column rep<br>signal"     | licate control signal" & "row replicate control                  | 27     |

|     |      |                        |            | (1)                        | The Parties' Positions                                           | 28     |

|     |      |                        |            | (2)                        | Construction                                                     | 30     |

|     |      |                        | g)         | "sizing said               | video image"                                                     | 3<br>8 |

|     |      |                        |            | (1)                        | The Parties' Positions                                           | 39     |

|     |      |                        |            | (2)                        | Construction                                                     | 40     |

|     |      |                        | h)         | "while main                | taining a video signal resolution "                              | 40     |

|     |      |                        |            | (1)                        | The Parties' Positions                                           | 41     |

|     |      |                        |            | (2)                        | Construction                                                     | 42     |

|     |      |                        | i)         | "generating said memory    | first control signals for readin g said video image in y system" | 44     |

|     |      |                        |            | (1)                        | The Parties' Positions                                           | 45     |

|     |      |                        |            | (2)                        | Construction                                                     | 46     |

|     |      |                        | j)         | "output colu control signa | mn address control signals" & "output row address als"           | 49     |

|      |     |       |       | (1)       | The Parties' Positions                       | 50     |

|------|-----|-------|-------|-----------|----------------------------------------------|--------|

|      |     |       |       | (2)       | Construction                                 | 52     |

|      |     |       | k)    | "pixel    | clock signal"                                | 54     |

|      |     |       |       | (1)       | The Parties' Positions                       | 55     |

|      |     |       |       | (2)       | Construction                                 | 56     |

|      | C.  | Me    | ans-l | Plus-Fun  | ction Limitations                            | 5<br>6 |

|      |     | 1.    | Pro   | per Cons  | struction of Means-Plus-Function Limitations | 56     |

|      |     | 2.    | Cla   | im Cons   | truction                                     | 58     |

|      |     |       | a)    | "timing   | g control means"                             | 59     |

|      |     |       |       | (1)       | The Parties' Positions                       | 59     |

|      |     |       |       | (2)       | Construction                                 | 61     |

|      |     |       | b)    | "image    | size/position control means"                 | 70     |

|      |     |       |       | (1)       | The Parties' Positions                       | 70     |

|      |     |       |       | (2)       | Construction                                 | 77     |

|      |     | 3.    | "fra  | ame buffe | er output control means"                     | 85     |

|      |     |       |       | (1)       | The Parties' Positions                       | 85     |

|      |     |       |       | (2)       | Construction                                 | 87     |

| III. | Con | clusi | on    |           |                                              | 90     |

#### I. Introduction

Please see Dkt. No. 90 for the claim-construction introduction and claim-construction legal principles. This order construes the fourth of four asserted patents. For brevity purposes, the introductory material and legal principles are included only in the first order, which construes the disputed terms of U.S. Patent No. 6,404,418.

# **II.** U.S. Patent No. 5,790,096

The '096 Patent, entitled "Automated Flat Panel Display Control System for Accomodating Broad Range of Video Types and Formats," issued on August 4, 1998 to Jaques R. Hill, Jr., from Application No. 707,338, filed on September 3, 1996. The '096 Patent has apparently been acquired by LG.

#### A. Overview

The '096 Patent "relates generally to flat panel display control systems, and more specifically to electronic control systems for accepting video signals of numerous formats and types, and for displaying such video signals on a wide variety of flat panel displays." '096 Patent, col. 1, lines 8-12. According to the abstract:

An electronics control system for full color and monochrome flat panel displays which automatically accommodates video signals of numerous types and formats, whether interlaced, non-interlaced, composite, or video signals with separated sync signals. Display of such video signals on a wide selection of flat panel display systems also is accommodated. Incoming and output video rates are asynchronous. Plug-in modules allow the system to convert video signals of numerous types and modes for display on any flat panel display

system. Images are both automatically, and under user control, up-sized and down-sized, positioned and oriented to fit the flat panel display being used. Color images are automatically reduced to grey scale monochrome when a monochrome flat panel display is being used. Push-pull A/D converter circuitry for digitizing color video signals is used to reduce cost while conserving power. A further power saving feature provides for automatic power down when video reception is interrupted, and power up when the video reception is reacquired.

# 1. Background

The '096 Patent cites numerous patents in explaining that the "use of flat panel displays" was "well known," and that various "electronic control systems for flat panel displays" could (1) "accommodate either interlaced or non-interlaced video signals, and \* \* \* separate out horizontal and vertical sync signals from a video signal," (2) "up-size a video image to fit a particular display, or center a small image within a larger screen," but not "perform [] sizing by varying the video rate as the video data is being stored," resulting in "lost" "pixel data" and "compromised" "image resolution," (3) "perform[] upsizing only, and \* \* \* not accommodate down sizing," (4) "only center ] an image in accordance with a table look-up of fixed data," (5) "accommodate color to color, and color to monochrome processing of video signals," (6) "use[] a color palette in supplying color signals to a computer CRT," but not "support NTSC, PAL or HDTV video formats," (7) perform "character conversion only," but not "color to monochrome conversions for graphics," (8) "accommodate one or more of PAL, HDTV, NTSC, and VGA RGB video signals in driving the display," (9) "automatically turn[] off a back light when video signals are not being received," but apparently not "turn[] the power back on when video signals reappear, or [provide] a power conserving sequencing system," (10) "exercis[e] pixel by pixel control to achieve high resolution displays of images," and (11) "automatically detect video formats and provide asynchronous video input and output," but not perform "asynchronous operation." The '096 Patent also cites another patent that "refers to and claims a color to grey scale conversion," but "fails to disclose how such a conversion is accomplished" and a patent that "discloses a portable computer system for plugging a number of displays into a same electronics board connector" but "cannot support NTSC, PAL or HDTV systems." '096 Patent, col. 1, line 15-col. 2, line 3.

# 2. Disclosure

The '096 Patent is said to disclose an "electronic control system" "which automatically identifies video signal type, format, and resolution, and adapts the video image for display on a wide variety of full color and monochrome flat panel display systems." '096 Patent, col. 2, lines 28-31. According to the '096 Patent:

In accordance with the invention, images on a flat panel display may be upsized, downsized, positioned and oriented automatically or through use of user controls. Further, monochrome to color, color to monochrome, color to color, and monochrome to monochrome video processing is accommodated. Still further, power to the electronic control system is sequentially turned on and off for power conservation as video appears, disappears, and reappears.

In addition, in accordance with the invention, video data may be received at the video rate and asynchronously output to a flat panel display at the display rate without any loss of resolution. Further, both video formats and types are automatically detected.

The present invention also provides plug-in modules for an input video connector at which video is received, for color frame buffers where image content is stored, and for a flat panel interface module to which a flat panel display attaches. All known flat panel displays, and video formats and types for flat panel

displays may be accommodated without compromising power conservation. The above and other aspects of the invention are summarized below.

'096 Patent, col. 2, lines 4-24.

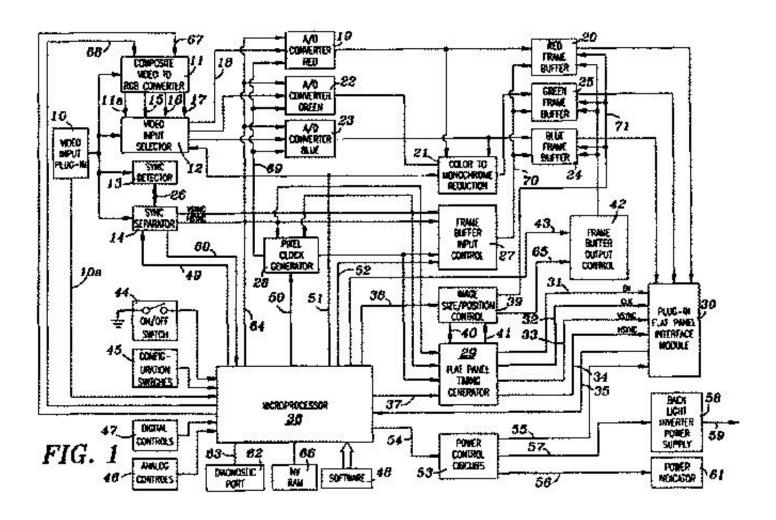

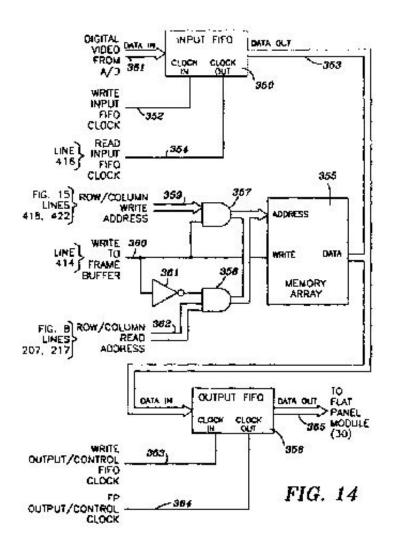

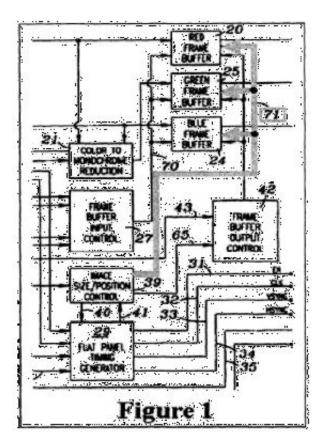

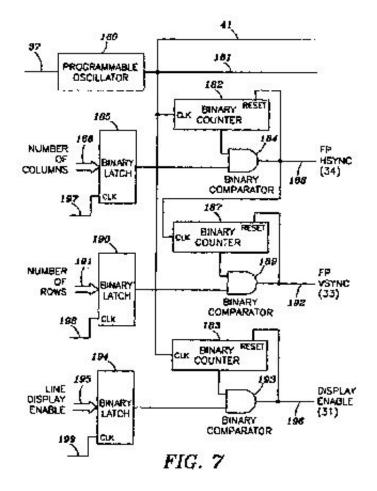

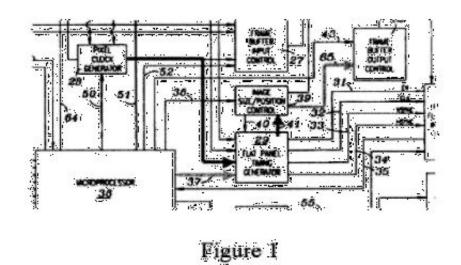

A "functional block diagram of an electronic control system" is illustrated in Figure 1 of the '096 Patent:

The '096 Patent describes the function of each component in some detail (including "logic schematic diagrams" of various components), and explains that the "electronic control system of Fig. 1 is comprised of both off-the-shelf commercial devices and customized devices," and "is a versatile system which may adapt to any format, and which is able to accommodate video resolutions up to at least 2048x2048 (rowsxcolumns)." '096 Patent, col. 13, lines 23-29. According to the '096 Patent, "[i]n operation, the microprocessor 36 controls all functions in the electronic control system of Fig. 1. By way of example, the microprocessor manages the power operation of the electronic control system, identifies the modes of the incoming video (interlace, non-interlace, resolution, type), measures the video signal timing parameters, controls the image size, position, orientation, focus and contrast, controls the timing of the electronic control system and flat panel display, controls backlight intensity, and controls color/monochrome transition processes." ' 096 Patent, col. 11, lines 40-49.

Those components and processes are discussed in more detail below as may be necessary or helpful to construe the disputed claim terms.

# 3. The Asserted Claims

LG asserts claim 21, which is independent and provides:

21. A system for controlling size, position and orientation of a video image presented on a flat panel display, and in electrical communication with a memory system having stored therein said video image, and receiving a video signal from a video source, which comprises:

timing control means receiving said video signal from said video source at a video signal data rate for generating therefrom enable, vertical synchronization, horizontal synchronization, and first clock signals for driving said flat panel display, generating column start, row start, column replicate, and row replicate control signals for sizing said video image while maintaining a video signal resolution, and generating first control signals for reading said video image in said memory system;

image size/position control means in electrical communication with said timing control means and responsive to said column start, row start, column replicate, and row replicate control signals and said first control signals for generating output column address control signals, output row address control signals for said memory system, and a pixel clock signal; and

frame buffer output control means in electrical communication with said timing control means, said memory system, said image size/position control means, and said flat panel display, and responsive to said pixel clock signal for reading said video image from said memory system.

'096 Patent, col. 31, line 59-col. 32, line 19.

# **B.** Claim Construction

# 1. Agreed Terms

The parties agree to constructions for the following terms:

| Agreed Construction  |

|----------------------|

| Generating from said |

| video signal.        |

|                      |

See Dkt. No. 64, at 27.

# 2. Disputed Terms

# a) "orientation"

The term appears in the preamble of claim 21 (the disputed term is in boldface):

21. A system for controlling size, position and **orientation** of a video image presented on a flat panel display, and in electrical communication with a memory system having stored therein said video image, and

receiving a video signal from a video source, which comprises: \* \* \* \*

'096 Patent, col. 31, line 59-col. 32, line 19 (emphasis added).

#### (1) The Parties' Positions

The parties propose the following constructions:

| LG                               | Hitachi                                                                 |  |  |  |

|----------------------------------|-------------------------------------------------------------------------|--|--|--|

| The extent to which a display is | The state of said video image describing whether it has been rotated 90 |  |  |  |

| rotated or flipped.              | degrees, 180 degrees, or mirrored.                                      |  |  |  |

| See Dkt. No. 64, at 23.          |                                                                         |  |  |  |

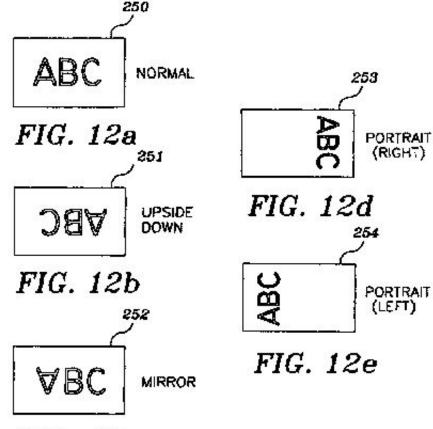

According to LG, this word is "straightforward." Dkt. No. 47, at 44. LG urges that the specification "provides a broad recitation of the manner in which an image may be displayed on a flat panel," namely, (1) "[t]he specification describes a system to permit adjustment of the way in which a visual representation of a video image is presented on a flat panel display, including controlling the size (how large the image appears), position (location of the image as presented), and orientation (extent to which the image is rotated or flipped)," and (2) Figures 12(a)-12(e) illustrate that "[a]n image may be 'normal' (250), rotated (253 or 254), flipped and rotated (251), and flipped so as to form a mirror image (252)." *Id.* at 44-45. LG contends "[t]he various 'orientations' shown in Figure 12 are simply examples of the claimed 'orientation' and the claim should not be limited to any particular orientation as urged by Defendants." *Id.* at 45. LG also argues that its proposed construction is "further supported by the common definition from extrinsic sources," i.e., dictionaries. *Id.*

Hitachi responds that the "specification discloses circuitry with a very limited ability to rotate/orient images by altering the order in which image pixel data is read from memory." Dkt. No. 48, at 15. Hitachi points to the specification at column 8, lines 57-64 in urging that "[t]he only *possible* orientations are 90 degrees, 180 degrees, or mirrored:"

The order in which data is read out of the frame buffers determines the form in which the image will be presented on the flat panel display screen. A timing signal that controls the reading of data from the frame buffer memory is output by control unit 39 to control unit 42 on line 65. The different *possible* presentation forms are described in more detail below in connection with the description of FIG. 12.

*Id.* at 15. Hitachi notes that "Figure 12 of the patent shows only 90 degree, 180 degree, and mirrored orientations" and cites column 9, lines 3-7, in arguing that "*only* these transformations are possible with the disclosed circuitry:"

By reversing the order of reading frame buffer rows and columns, a video image may be presented in portrait form. *That is, rotated by ninety degrees*. Further, by reading the columns from the right-most to the left-most column, the image can be presented in *mirror-image* form.

*Id.* at 15. Hitachi contends LG's "proposed construction would allow for orientations at any angle from 0 to 360 (deg.)," which would be "impossible with the disclosed circuitry [because] the specification neither describes nor enables such orientations." *Id.* at 15-16. Under LG's construction, Hitachi urges, "claim 21 is invalid under Section 101 (lack of utility as non-operational) and Section 112, para. 1 (as both not described

and not enabled)." *Id.* at 16. Finally, Hitachi argues that LG's "reliance on common English dictionary definitions is inappropriate \* \* \* because the limited disclosure in the specification does not support a broad, general-purpose definition of 'orientation.' " *Id.* at 16.

LG replies that Hitachi is "attempting to limit [its] construction to the disclosed embodiment in the '096 Patent," which is impermissible because "there is no language in claim 21 to limit the term 'orientation' \* \* \* [and] a review of the other claims of the '096 patent confirms this." Dkt. No. 55, at 38. LG notes that "independent claim 27 recites 'orienting said display image,' while dependent claim 28 recites 'wherein said display image is one or more of an upside down image form, a portrait image form, a mirror-image form, and a rotated image form.' "*Id*. LG concludes that "the 'orientation' set forth in independent claim 27 is presumed to be of broader scope than that disclosed in dependent claim 28 and terms should be construed consistently among the claims." Dkt. No. 55, at 38, *citing* Acumed L.L.C. v. Stryker Corp., 483 F.3d 800, 806 (Fed.Cir.2007); Rexnord Corp. v. Laitram Corp., 274 F.3d 1336, 1342 (Fed.Cir.2001).

Finally, LG argues that Hitachi's proposed construction "would exclude one of the forms-namely, the 'NORMAL' orientation labeled as Fig. 12a-of the very embodiment that [Hitachi] cite[s] as support." Dkt. No. 55, at 38. LG asserts that its own proposed construction "encompasses the presentation forms shown in Figure 12 (namely 0, 90, 180, and 270 degrees and mirror-image) and comports with the ordinary meaning of the term." *Id.* at 39.

# (2) Construction

[1] The non-asserted claims use this term in much the same way as asserted claim 21, *i.e.*, to describe the appearance of a "video image." Overall, though, the claim language provides little guidance regarding the meaning of "orientation," beyond distinguishing other characteristics of "video image" appearance, namely, size and position.

It is clear from the claims and specification, however, that "size, position and orientation" refer to how a video image is presented on a video display. What "orientation" means is more clear when discussed with "size" and "position." According to the specification, "size" refers to just that, *i.e.*, the size of the video image on the display, "position" refers to how the video image fits on the video display, and "orientation" refers to the direction of the video image on the display.

For example, with respect to sizing, the specification explains that "the video image may be up-sized or down-sized." '096 Patent, col. 2, lines 48-49; *see* id. at col. 9, lines 16-19 ("For example, in order to *stretch or zoom an image horizontally*, the control unit 42 will repeat a column address as often as required to achieve the desired horizontal stretching." (emphasis added)); col. 9, lines 12-20 ("In addition to controlling the reading of video data out of the frame buffers to achieve the above video presentations, the control unit 42 also addresses the frame buffer memory locations in a manner to *up-size or down-size an image on the display screen*. In the case of *vertical stretching or zooming*, a row address is repeated in like manner." (emphasis added)); col. 25, lines 33-40 ("The remaining switch pairs operate similarly, with switches 324 and 325 controlling the movement of the video image up or down, *switches 328 and 329 controlling the horizontal expansion or contraction of the video image*." (emphasis added)); and col. 9, lines 21-24 ("The *up and down sizing* is independent of whether the image output is being presented 'normally', upside-down, mirrored, in portrait form (left or right), or in any other presentation form." (emphasis added)).

With respect to positioning, the specification explains that "the image can be positioned left-to-right, right-to-left, or up or down" so as to "center the video image on the display screen." '096 Patent, col. 9, lines 30-31, 66-67; *see* id. at col. 14, line 63-col. 15, line 2 ("More particularly, at logic step 101, the pixel clock generator 28 is programmed to assume a 640 column video signal, the counters of the frame buffer input control unit 27 and the frame buffer output control unit 42 are set to zero, and the image size/position control unit 39 is *programmed to accom-modate a 1-to-1 sized image positioned in the upper left image corner at row 0 and column 0.*" (emphasis added)); col. 25, lines 33-40 ("The remaining switch pairs operate similarly, with *switches 324 and 325 controlling the movement of the video image up or down*, switches 328 and 329 controlling the horizontal expansion or contraction of the video image." (emphasis added)).

With respect to orientation, the specification explains that "the video image may be rotated in 90 (deg.) increments for presentation in portrait form, or rotated 180 (deg.) to accommodate LCD displays with different optical vertical viewing cycles, or presented in mirror-image form for use in overhead projection systems." '096 Patent, col. 2, lines 53-57. The specification provides in Figure 12, "a graphic illustration of the variety of image presentations that are provided by the electronic control system." '096 Patent, col. 24, lines 42-44.

FIG. 12c

According to the specification, "[p]resentation 250 shows a straight up and down image, while presentation 251 presents an upside down image. Further, presentation 252 shows a mirror image. The above described portrait images are shown in presentations 253 and 254 as respectively a portrait right image and a portrait left image." '096 Patent, col. 24, lines 44-49.

For example, the specification explains, a "video image" may be "displayed upside down on the display screen." Apparently, "[t]his form of display is particularly useful with LCD displays that have a vertical viewing angle that is opposite to that of the viewing angle of user. By reversing the order of reading frame buffer rows and columns, a video image may be presented in portrait form. That is, rotated by ninety degrees. Further, by reading the columns from the right-most to the left-most column, the image can be presented in mirror-image form. A mirror-image [p]resentation is especially useful in overhead projection viewing, and in other applications where the image is first viewed by the user as a reflection in a mirror as with television teleprompters." '096 Patent, col. 9, lines 1-12; *see* id. at col. 9, lines 21-24 ("The up and down sizing is independent of whether the image output is being presented 'normally', upside-down, mirrored, in portrait form (left or right), or in any other presentation form.").

Thus, as the parties note, video image orientation refers to the degree of rotation of the video image, or how the video image is mirrored. The dispute appears to concern whether the claim is limited to the 90 (deg.) or 180 (deg.) orientations and mirroring disclosed in the specification, e.g., those of Figure 12. The Court finds that it is not. One reason is because Figure 12 also discloses 0 (deg.) (normal) and 270 (deg.) orientations. Another reason is because the specification describes those orientations as "possible" orientations. See '096 Patent, col. 8, lines 62-64 ("The different possible presentation forms are described in more detail below in connection with the description of FIG. 12 [a "preferred embodiment."]) (emphasis added); '096 Patent, col. 3, lines 30-35 ("The accompanying drawings, which are incorporated in and constitute a part of the specification, illustrate a preferred embodiment of the invention, and together with the general description given above and the detailed description of the *preferred embodiment* given below, serve to explain the principles of the invention.") (emphasis added); '096 Patent, col. 28, lines 31-40 ("The invention has been described and shown with reference to particular embodiments, but variations within the spirit and scope of the general inventive concept will be apparent by those skilled in the art. Accordingly, it should be clearly understood that the form of the invention as described and depicted in the specification and drawings is illustrative only, and is not intended to limit the scope of the invention. All changes which come within the meaning and range of the equivalence of the claims are therefore intended to be embraced therein.").

Hitachi urges that "orientations at any angle from 0 to 360 (deg.)" are "impossible with the disclosed circuitry." According to Hitachi, LG's proposed construction would render the claim as lacking utility under s. 101 or invalid under s. 112(1) as both not appropriately supported by the written description and not enabled. Presumably, Hitachi refers to angles other than the 0 (deg.), 90 (deg.), 180 (deg.) and 270 (deg.) angles disclosed in the specification. Regardless, Hitachi provides no support for the assertion, whether from intrinsic or extrinsic evidence. *See* Talbert Fuel Sys. Patents Co. v. Unocal Corp., 275 F.3d 1371, 1376 (Fed.Cir.2002) ("We agree that a construction that renders the claimed invention inoperable should be viewed with extreme skepticism. However, Talbert did not demonstrate inoperability or provide any basis for judicially interpreting the claim to adjust the temperature range that Talbert states is the inoperable limitation." (citation omitted)). In any event, "[c]onstruction of the claims here is not so difficult a problem as to require resort to the validity maxim." MBO Labs., Inc. v. Becton, Dickinson & Co., 474 F.3d 1323, 1332 (Fed.Cir.2007) ("[V]alidity construction should be used as a last resort, not a first principle \* \* \*.").

Thus, the Court construes "orientation" to mean "the extent to which a display is rotated or flipped."

# b) "video image"

This phrase appears in claim 21 (the disputed term is in boldface):

21. A system for controlling size, position and orientation of a **video image** presented on a flat panel display, and in electrical communication with a memory system having stored therein said video image, and receiving a video signal from a video source, which comprises:

timing control means receiving said video signal from said video source at a video signal data rate for generating therefrom enable, vertical synchronization, horizontal synchronization, and first clock signals for driving said flat panel display, generating column start, row start, column replicate, and row replicate control signals for sizing said **video image** while maintaining a video signal resolution, and generating first control signals for reading said **video image** in said memory system;

image size/position control means \* \* \*; and

frame buffer output control means in electrical communication with said timing control means, said memory system, said image size/position control means, and said flat panel display, and responsive to said pixel clock signal for reading said **video image** from said memory system.

'096 Patent, col. 31, line 59-col. 32, line 19.

#### (1) The Parties' Positions

The parties propose the following constructions:

| LG                                            | Hitachi                                              |

|-----------------------------------------------|------------------------------------------------------|

| Data used to generate a visual representation | A video frame described by a set of rows and columns |

| of a video frame.                             | generated from the video signal.                     |

See Dkt. No. 64, at 11.

LG urges the terms "video image," "video signal" and "video signal data rate" are "interrelated because the flat panel display control system of the '096 patent visually displays video images on a flat panel screen by storing and processing data carried on a video signal received at a data rate." Dkt. No. 47, at 46. With respect to the first term, *i.e.*, "video image," LG argues this term "clearly requires a construction that includes a video image stored in a memory system for later processing and presentation on a flat panel display," *i.e.*, as illustrated in Figure 12. *Id*. According to LG, Hitachi misses that "key point," which "lies at the center of the dispute." *Id*. In LG's view, "[o]f course, what is stored in a memory is data (i.e., logical 1s and 0s) that can be read by a computer system in which the memory belongs," and the "video image" "consequently must include the 'data' that can be stored or manipulated by the system." *Id*. Thus, LG contends "video image" "refers to data that is used to generate a visual representation ultimately displayed on a flat panel display." *Id*.

Hitachi responds that the patent "defines a 'video image' as '[a] set of rows (lines) and columns that describe a video image. Also referred to as a video frame.' " Dkt. No. 48, at 11 (quoting '096 Patent, col. 4, lines 31-

32). Hitachi further asserts that "this term is important to claim 21 because the claim has several other limitations directed to 'said video image,' including: \* \* \* 'a memory system having stored therein *said video image;*' 'for sizing *said video image;*' 'for reading *said video image* in said memory system;' and 'reading *said video image* from said memory system.' " Id. Hitachi urges that "[t]he difference between 'a' and 'said' in [LG's] proposed construction is significant, because it improperly broadens the claim" and that " 'said video image' means 'the same video image' not just 'a video image.' " Id.

Hitachi states that LG "hopes to argue that the rest of the claim need not deal with the *same* 'said video image,' so long as some of the 'data used to generate' the image (*i.e.*, only part of the image, or even part of the data in some manipulated or altered form) satisfies the remainder of the claim." Dkt. No. 48, at 12. Hitachi argues, however, that "the same 'said video image' must satisfy all the requirements of claim 21" and further urges that its "proposed construction defines the video image to be a video frame, consistent with the rest of claim 21 because the same video image is used throughout the claim." *Id*.

Hitachi contends that "[u]nder [LG's] construction, every electronic signal disclosed in the '096 patent is a 'video image,' as all signals, in some way or another, could be argued to be 'used' to generate the eventual and ultimate result of the display of a video frame." Dkt. No. 48, at 12 n. 10. Hitachi asserts, "[t]his is too broad and not supported by the clear language of the specification" and "the issue is whether the video image is exactly that (the image itself), as opposed to (a) merely a subset of some (but not necessarily all) of the complete set of image data, or (b) some other data that is not the image itself, but that is merely used 'to generate a video frame.' "*Id.* Hitachi concludes that LG's "broad construction contradicts the remainder of claim 21 by opening the door to something other than 'said video image is 'generated from the video signal,' " as described in the '096 Patent specification at column 2, lines 12-17 and 28-31. Id.

LG replies that Hitachi's "construction of 'video image' is based on a misreading of the '096 patent," which "defines a '*Frame*' (not 'video image') as 'a set of rows (lines) and columns that describe a video image. Also referred to as a video frame." Dkt. No. 55, at 39. LG urges that "a 'video frame' can describe a video image; thus, the video frame contains data that is used to generate a visual representation of the video image." *Id* . LG also argues that "[t]he specification, including Figures 3a and 3b (*e.g.*, the 'image content' signals), of the '096 patent further support [LG's] construction that 'video image' is a 'visual representation' of the *data* in a video signal." Id.

LG characterizes Hitachi's construction as "nonsensical" because it "excludes the embodiment of the invention disclosed in the '096 patent, and even contradicts their own description of the claim." Dkt. No. 55, at 39. Specifically, LG urges that Hitachi's construction, "which [Hitachi] admit[s] cannot be 'merely a subset of some (but not necessarily all) of the complete set of image data'-precludes these very aspects of the invention, because, for example, by down-sizing the video image, the device necessarily presents a subset of the image data (by removing portions of the image to shrink it)." *Id.* at 40.

With respect to Hitachi's "a video image" and "said video image" argument, LG "agrees that the term 'said video image' needs to be used consistently through the claim," and contends "this is the reason why the term 'video image' should be construed to be 'data used to generate a visual representation of a video frame.' " *Id*.

Finally, LG argues that "Claim 21 requires that the element satisfying the 'video image' limitation be 'presented on a flat panel display' (Col.31:60), 'stored' in 'a memory system' (Col.31:61-62), 'siz[ed]' when presented on the flat panel display (Col.32:3), and 'read[]' from 'said memory system' (Col. 32:5-6 & 18-

19) ." LG further argues that "[o]nly [its] proposed construction satisfies these limitations, because 'data' is what is stored and read from the claimed memory system and presented and sized on the flat panel display to provide the video image viewed by the user." Dkt. No. 55, at 40. LG also contends that its "construction is not 'too broad' \*-\*-\* because it is expressly limited to data that is used to create the visual representation of a video frame." *Id*.

# (2) Construction

[2] Turning first to the language of the claim at issue, claim 21, FN1 the preamble makes a number of things clear:

FN1. Of the other claims of the '096 Patent, only claim 3 recites a "video image," and does so only once, *i.e.*, in the context of a "image size/position control means in electrical communication with said microprocessor means, said frame buffer means, and said flat panel timing generator means for generating image control signals to control size, position and orientation of a *video image* presented on said flat panel display." (emphasis added)

21. A system [1] for controlling size, position and orientation of a video image presented on a flat panel display, and [2] in electrical communication with a memory system having stored therein said video image, and [3] receiving a video signal from a video source, which comprises: \* \* \*

'096 Patent, col. 31, line 59-col. 32, line 19 (numbering added). Thus, the "video image" may have a "size, position and orientation." The "video image" may be stored in, and may be read in and from, "a memory system," which supports the "data" aspect of LG's proposed construction. Also, a "video image" is not the same thing as a "video signal."

The body of claim 21 further makes clear that the "video image" is subject to "sizing" by "column start, row start, column replicate, and row replicate control signals," is read in memory by "first control signals," and is read out of memory by a "frame buffer output control means." This language seemingly supports Hitachi's proposed construction.

The focus thus turns to the specification, which provides the following defined terms:

Video Line: A horizontal video line also referred to as a row or video row.

Frame: A set of rows (lines) and columns that describe a video image. Also referred to as a video frame.

Interlace: Interlaced video is where a first frame of video contains only the odd rows (video lines), e.g., 1, 3, 5, etc., and the second frame of video contains only the even rows (video lines), e.g., 2, 4, 6, etc. Interlaced video requires two complete frames of video to completely describe an image.

'096 Patent, col. 4, lines 29-38. According to these definitions, a video image is ultimately made up of rows and columns. These rows and columns may be arranged in one (non-interlaced) or more (interlaced) sets, called video frames. *See also* '096 Patent, col. 2, lines 40-44 ("[T]he microprocessor of the electronic control system can automatically detect and accommodate a change in format, for example a change between NTSC and PAL formats, and determine whether a video image is interlaced or non-interlaced."). Thus, a video image is made up of one or more video frames, which are in turn made up of rows and columns. *See also* '096 Patent, col. 21, lines 4-6 ("The latch in turn receives a count of the number of flat panel columns").

in a video image from the microprocessor 36 on bus 186."); id. at col. 21, lines 11-14 ("A second input of the comparator 189 is connected to the output of a binary latch 190, which receives a count of flat panel rows in a video image on bus 191.").

But the specification also describes these columns (and presumably rows), on a more fundamental level, as data. See '096 Patent, col. 23, lines 31-33 ("That is, one converts odd columns while the other converts even columns of video data."). In other words, a "video image" is data that is processed to generate an on-screen video display. See '096 Patent, col. 8, line 65-col. 9, line 1 ("[I]f the control unit 42 reads the frame buffer video data beginning at the last line and then proceeding to the first, the video image will be displayed upside down on the display screen."); id. at col. 9, lines 12-13 ("controlling the reading of video data out of the frame buffers to achieve the above video presentations"); id. at col. 20, lines 36-44. ("[W]hen a monochrome video signal is to be displayed on a flat panel color display, green video data is fed from the green color A/D converter 22, through the color to monochrome reduction device 21 and green color frame buffer 25, to the flat panel interface module 30 of Figure 1. Thereafter, under control of the microprocessor 36, the green video data is supplied to the red, green and blue inputs of the flat panel display to have the monochrome image displayed in black and white."); id. at col. 26, lines 22-25 ("The video image data for the flat panel display appears at the output of FIFO 356. The output FIFO allows video data to continue to be supplied to the flat panel display when the memory array 355 is unavailable during write cycles."); id. at col. 27, lines 55-63 ("With the frame buffers operating in a fully asynchronous manner, video data may be read out of the frame buffers and through the output FIFO 356 to the flat panel display. During the brief 'burst write' time, the frame buffer is being written into, and therefore cannot be read. However, the output FIFO contains enough video data so that output to the flat panel display is not interrupted. The output FIFO is not filled during the frame buffer write time, but the FIFO continues to output data to the flat panel display."); id. at col. 26, line 66-col. 27, line 1 ("In operation, the microprocessor 36 programs the latches 405 and 408 with the start and stop location of the incoming video image."); id. at col. 18, lines 22-24 ("the microprocessor 36 receiving the video format or mode of the incoming video data from the video input connector 10"). See also '096 Patent, col. 9, lines 34-36 ("[T]he microprocessor 36 accesses application software stored in memory unit 48 to process video signals for display on the flat panel display screen (not shown)."). Thus, both parties are, in part, correct.

Nevertheless, interpreting this term at its most basic level makes the most sense in the context of the claims. Again, in claim 21, "video image" is stored in memory, and in the specification, the video image is stored in memory as data, *i.e.*, video column and line data is stored in various memory addresses. *See, e.g.*, '096 Patent, col. 9, lines 13-16 ("In addition to controlling the reading of video data out of the frame buffers to achieve the above video presentations, the control unit 42 also addresses the frame buffer memory locations in a manner to up-size or down-size an image on the display screen."); id. at col. 9, lines 26-29 ("[T]he control unit 42 also positions an image on the flat panel display screen by addressing the frame buffer memory locations commencing at any location in the memory space."); id. at col. 20, lines 61-64 ("This clock signal is the same clock signal as that used to create the flat panel timing, and also is used to create frame buffer memory addresses of output video data."). The "video image" is also sized, positioned and oriented, and the specification explains that such manipulation occurs by changing how the data is read out of memory. *See, e.g.*, '096 Patent, col. 22, lines 25-28 ("In operation, the image size/position control unit 39 provides image positioning, image size, and image orientation by modifying the memory addresses that are presented to the frame buffers 20, 24, and 25.").

The claims also indicate that the data making up the "video image," first recited in the preamble as stored in memory, are the same data that are, in the body of the claim, read in and from memory. The data may be

used more than once, of course, for up-sizing the video image to fit a screen. *See* '096 Patent, col. 9, lines 12-16 ("In addition to controlling the reading of video data out of the frame buffers to achieve the above video presentations, the control unit 42 also addresses the frame buffer memory locations in a manner to up-size or down-size an image on the display screen. For example, in order to stretch or zoom an image horizontally, the control unit 42 will repeat a column address as often as required to achieve the desired horizontal stretching. In the case of vertical stretching or zooming, a row address is repeated in like manner."). For down-sizing, the converse is true, *i.e.*, data (or a column of data) is skipped.

Also, the specification explains that if a color video image is to be displayed on a monochrome screen, some of the video image data is processed to create new weighted image data. The specification explains that "[i]f color video is to be displayed on a monochrome display, the red, blue and green video signals received by the device 21 must be reduced to monochrome video according to a weighting or color mixing standard," such as that of Table 1:

| TABLE I    |      |       |      |  |  |  |

|------------|------|-------|------|--|--|--|

| NTSC       | 5/16 | 9/16  | 2/16 |  |  |  |

| Weighting  | Red  | Green | Blue |  |  |  |

| Equal      | 5/16 | 6/16  | 5/16 |  |  |  |

| Weighting  | Red  | Green | Blue |  |  |  |

| Green Only | 0/16 | 16/16 | 0/16 |  |  |  |

|            | Red  | Green | Blue |  |  |  |

| User       | ?/16 | ?/16  | ?/16 |  |  |  |

| Defined    | Red  | Green | Blue |  |  |  |

'096 Patent, col. 7, lines 20-32. See id. at col. 8, lines 34-36 ("The microprocessor 36 reads the configuration switches 45 to control the weighting (or mixing) of the colors by the color to monochrome reduction device 21."); id. at col. 20, lines 8-23 ("In operation, when color video information is to be displayed on a monochrome flat panel display, one of the equations set forth in Table I above is programmed by the microcontroller 36 into the color to monochrome reduction device 21, and weighting values for red, blue and green color are written by the microprocessor into the latch registers 164, 166, and 168. More particularly, latch 164 contains the weighting for the color red, latch 166 contains the weighting for the color green, and latch 168 contains the weighting for the color blue. The AND gates 163, 165 and 167 transition to a logic one level only when both a color video data signal and a weighting for that color are received. Thus, only weighted color values are allowed to pass to OR gate 169, where the color data is mixed only in the amounts indicated by the weightings. The output of OR gate 169 is one bit of monochrome grey scale."). In other words, less than all of the video image data, or further-processed data, may be used to generate a video display. Hitachi's argument that video image data cannot be "a subset of some (but not necessarily all) of the complete set of image data," must therefore be rejected. Hitachi's argument that "video image" cannot connote data that "is not the image itself, but that is merely used 'to generate a video frame,' " must similarly be rejected.

# Thus, the Court construes the term "video image" to mean "data that forms a visual representation when displayed."

#### c) "video signal"

This phrase appears in claim 21 (the disputed term is in boldface):

21. A system for controlling size, position and orientation of a video image presented on a flat panel display, and in electrical communication with a memory system having stored therein said video image, and receiving a **video signal** from a video source, which comprises:

timing control means receiving said **video signal** from said video source at a **video signal** data rate for generating therefrom enable, vertical synchronization, horizontal synchronization, and first clock signals for driving said flat panel display, generating column start, row start, column replicate, and row replicate control signals for sizing said video image while maintaining a **video signal** resolution, and generating first control signals for reading said video image in said memory system;

image size/position control means \* \* \*; and

frame buffer output control means \* \* \*.

'096 Patent, col. 31, line 59-col. 32, line 19 (emphasis added).

# (1) The Parties' Positions

The parties propose the following constructions:

| LG                        | Hitachi                                                                            |

|---------------------------|------------------------------------------------------------------------------------|

| A signal containing data  | An electronic signal containing information specifying the location and brightness |

| used to generate a visual | of each point on a display, along with the timing signals to place the image       |

| representation of a video | properly on the display. Video signal formats include VGA, SVGA, XGA, NTSC,        |

| frame.                    | PAL and SECUM video.                                                               |

See Dkt. No. 64, at 25.

LG urges its proposed construction "to ensure consistency between construction of various terms within claim 21, and preserve the interconnection between the terms 'video image' and 'video signal' as claimed." Dkt. No. 47, at 47. According to LG, Hitachi's proposed construction "not only fails to preserve continuity among the claim terms, but also injects unnecessary confusion into a term that is otherwise well-understood." *Id*. LG urges that "including a list of specific information contained within the 'video signal,' such as 'location and brightness of each point on a display' and 'timing signals to place the image properly on the display' will not assist the finder of fact in understanding this relatively simple term, and such limitations are not requirements of the clear language." *Id*.

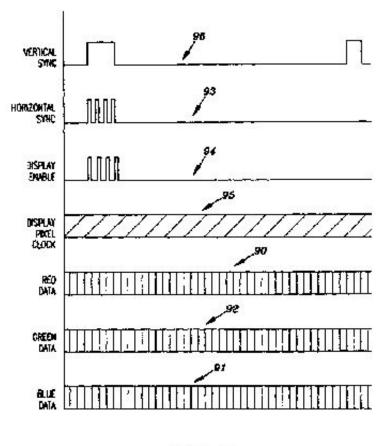

Hitachi urges that "[t]he specification defines a 'video signal' as including 'formats and types' \* \* \* and further defines a 'video format' as a signal including timing and brightness signals:

Video Format (Modes): The timing characteristics of a video type including number of rows and columns, frames per second, and whether the video lines are interlaced or noninterlaced. Formats for composite video include (i) NTSC11 (National Television Standards Committee) with 525 lines of video interlaced at 60 Hz, (ii) PAL (Phase Alternating Line) with 625 lines of video interlaced at 50 Hz, (iii) HDTV (High Definition Television) which currently has no universally accepted format but as used herein has 1125 lines of video at 100 Hz, and (iv) numerous variations of NTSC and PAL. Formats for component video include (i) RGB (sync on green) in NTSC, PAL or other video format; (ii) RGB (sync on green) in non-interlaced format at

different numbers of lines and columns; (iii) VGA with 640 x 480 non-interlaced video at 60 Hz, 720 x 400 non-interlaced video at 60 Hz, and 640 x 350 non-interlaced video at 60 Hz, (iv) SVGA with 800 x 600 non-interlaced video, (v) XGA with 1024 x 768 non-interlaced video, and (vi) SXGA with 1280 x 1024 non-interlaced video.

Dkt. No. 48, at 13 (citing '096 Patent, col. 4, lines 45-65).

Hitachi contends "[t]he specification defines 'video type' as a signal that includes picture signals and timing signals" and cites "several examples wherein the timing signals are carried within the video signal." Dkt. No. 48, at 13. Hitachi urges that its construction "is also consistent with several technical dictionary definitions" and notes that it comports with "the only embodiment described in the '096 patent." Id. at 13-14. Finally, Hitachi asserts that LG's construction "would read on non-video signals, such as synchronization or memory read/write signals, which do not contain the actual video data, but which are only used (in some unspecified way) to generate a displayed frame." Id. at 14.

In response, LG argues that Hitachi's "attempt to shoehorn the definitions of other phrases-namely, 'Video Type' and 'Video Format'-into the 'video signal' claim term should be rejected [because] [n]either the claim nor the specification requires such limits on the 'video signal' claim term." Dkt. No. 55, at 41. LG notes that "in the 'Video Format' section of the specification quoted by [Hitachi], the passage includes a reference to 'HDTV (High Definition Television) which *currently has no universally accepted format* but as used herein has 1125 lines of video at 100 Hz ...' " *Id*. LG argues that Hitachi failed "to include 'HDTV in its proposed construction even though the specification discloses that such signals can be accepted by the claimed system in Table VI." *Id*. Finally, LG urges that its construction does not read on non-video signals because it "is expressly directed to video signals by requiring such signals to contain 'data used to generate a visual representation of a video frame'- *i.e.*, a signal containing a 'video image.' " *Id*.

# (2) Construction

[3] In claim 21, the "video signal" is received by the "system" from a "video source" "at a video signal data rate." The claim language provides no additional guidance in construing this term.

The specification explains that "[t]he invention relates generally to flat panel display control systems, and more specifically to electronic control systems for accepting video signals of numerous formats and types, and for displaying such video signals on a wide variety of flat panel displays." '096 Patent, col. 1, lines 8-12. Hitachi views this language as defining a "video signal" in terms of formats and types, thus invoking various limitations from the specification-defined term "video format:"

Video Format (Modes): The timing characteristics of a video type including number of rows and columns, frames per second, and whether the video lines are interlaced or non-interlaced. Formats for composite video include (i) NTSC (National Television Standards Committee) with 525 lines of video interlaced at 60 Hz, (ii) PAL (Phase Alternating Line) with 625 lines of video interlaced at 50 Hz, (iii) HDTV (High Definition Television) which currently has no universally accepted format but as used herein has 1125 lines of video at 100 Hz, and (iv) numerous variations of NTSC and PAL. Formats for component video include (i) RGB (sync on green) in NTSC, PAL or other video format; (ii) RGB (sync on green) in non-interlaced format at different numbers of lines and columns; (iii) VGA with 640x480 non-interlaced video at 60 Hz, 720x400 non-interlaced video at 60 Hz, and 640x350 non-interlaced video at 60 Hz, (iv) SVGA with 800x600 non-interlaced video, (v) XGA with 1024x768 non-interlaced video, and (vi) SXGA with

1280x1024 non-interlaced video.

'096 Patent, col. 4, lines 45-65.

The specification describes many video signal aspects. *See, e.g.,* '096 Patent, col. 2, lines 28-31 ("An electronic control system is disclosed which automatically identifies video signal type, format, and resolution, and adapts the video image for display on a wide variety of full color and monochrome flat panel display systems."); '096 Patent, col. 5, lines 16-17 ("a full color composite video signal"); id. at col. 5, line 64 ("analog red, green and blue video signals"); id. at col. 6, lines 22-23 ("identify the type of the video signal being received"), col. 10 lines 34-35 ("high rate video signals"); id. at col. 11, line 45 ("the video signal"); id. at col. 12, lines 58-59 ("extracting synchronization signals from the incoming video signal"); id. at col. 14, lines 5-7 ("extracts the horizontal sync and vertical sync signals from the video signal"); id. at col. 11, lines 43-45 ("identifies the modes of the incoming video (interlace, non-interlace, resolution, type), measures the video signal timing parameters"); id. at col. 16, lines 19-21 ("low amplitude video signal" *per se*. The claim simply recites "video signal," not "video signal format" or "video signal timing" or some other "video-signal"-related term. In short, Hitachi's argument misses the point of the video signal, namely, to carry video data.

# Thus, the Court construes the term "video signal" to mean "a signal that contains data that forms a visual representation when displayed."

d) "video signal data rate"

This phrase appears in claim 21 (the disputed term is in boldface):

21. A system for controlling size, position and orientation of a video image presented on a flat panel display, \* \* \*, which comprises:

timing control means receiving said video signal from said video source at a **video signal data rate** for generating therefrom enable, vertical synchronization, horizontal synchronization, and first clock signals for driving said flat panel display, generating column start, row start, column replicate, and row replicate control signals for sizing said video image while maintaining a video signal resolution, and generating first control signals for reading said video image in said memory system;

image size/position control means \* \* \*; and

frame buffer output control means \* \* \*.

'096 Patent, col. 31, line 59-col. 32, line 19 (emphasis added).

#### (1) The Parties' Positions

The parties propose the following constructions:

| LG                   | Hitachi                                                             |

|----------------------|---------------------------------------------------------------------|

| The frequency of the | The frequency of the signal that carries the video data being input |

| video signal.        | from the video source.                                              |

#### See Dkt. No. 64, at 26.

According to LG, "[t]he parties seem to agree that [this] phrase \* \* \* is associated with a video signal frequency," but Hitachi limits the claim to being 'associated only with a "number that reflects the vertical frequency.' " Dkt. No. 47, at 47-48. In LG's view, "[t]he video signal data rate also may include other information, such as data related to frame rate, pixel rate, and bandwidth, which may be described more generally as 'frequency' information." *Id*. at 48.

In response, Hitachi altered its proposed claim construction from "the number that reflects the vertical frequency of the video signal from the video source" to the construction noted above. Dkt. No. 48, at 14. Hitachi urges that LG's "construction is vague in that it does not expressly require the 'video signal *data* rate' to be the frequency of the video *data*" and may cause confusion "in the scenario in which the video signal being input from the video source includes nondata frequencies, such as timing signal frequencies." *Id*.

In response, LG notes Hitachi's altered claim construction in suggesting "that the dispute between the parties has been narrowed or eliminated." Dkt. No. 55, at 42. Regardless, LG urges that "it is clear from the plain language of the claim that the video signal is received from a video source; thus, [Hitachi's] inclusion of this phrase in its proposed construction is superfluous and would only confuse the jury." *Id*.

#### (2) Construction

[4] The parties' dispute appears to be resolved. Claim 21 expressly calls for the "video signal" to be "from a video source at a video signal data rate." Thus, there is no need to repeat that in construing this term. Further, it is the signal itself that is received at that rate. All the data carried by the signal are thus received at that rate, as well. In any event, Hitachi's reference to "the signal that carries the video data" is understood to refer to the claimed "video signal." Thus, there appears to be no substantive difference between the parties' positions.

The specification does not use this term, nor the term "data rate." The specification does, however, refer to a "video rate," which appears to be the same thing. *See* '096 Patent, col. 2, lines 12-15 ("[I]n accordance with the invention, video data may be received at the video rate and asynchronously output to a flat panel display at the display rate without any loss of resolution."). For example, the specification explains, that "[t]he microprocessor 36 also works in co-operation with the A/D converters 19, 22, and 23 to accommodate high rate video signals in the range of 25 to 40 MHz." ' 096 Patent, col. 10, lines 33-35. In other words, the video rate refers to the video signal frequency, as the parties urge.

# Thus, the Court construes the term "video signal data rate" to mean "the frequency of the video signal."

# e) "flat panel display"

This phrase appears in claim 21 (the disputed term is in boldface):

21. A system for controlling size, position and orientation of a video image presented on a **flat panel display**, and in electrical communication with a memory system having stored therein said video image, and receiving a video signal from a video source, which comprises:

timing control means receiving said video signal from said video source at a video signal data rate for generating therefrom enable, vertical synchronization, horizontal synchronization, and first clock signals for driving said **flat panel display**, generating column start, row start, column replicate, and row replicate control signals for sizing said video image while maintaining a video signal resolution, and generating first control signals for reading said video image in said memory system;

image size/position control means \* \* \*; and

frame buffer output control means in electrical communication with said timing control means, said memory system, said image size/position control means, and said **flat panel display**, and responsive to said pixel clock signal for reading said video image from said memory system.

'096 Patent, col. 31, line 59-col. 32, line 19 (emphasis added).

# (1) The Parties' Positions

The parties propose the following constructions:

| LG                                                           | Hitachi                                   |  |  |  |

|--------------------------------------------------------------|-------------------------------------------|--|--|--|

| A display device other than a cathode-ray tube (CRT),        | An electronic display with a package      |  |  |  |

| having flat front, including liquid crystal (LCD) and plasma | thickness that is a small fraction of the |  |  |  |

| flat panel technology.                                       | display's height or length.               |  |  |  |

| $C \rightarrow DD = 4.5 \pm CC \rightarrow 20$               |                                           |  |  |  |

See PR 4-5d CC at 28.

According to LG, "[t]he specification repeatedly describes the term' flat panel display' as including liquid crystal (LCD), electroluminescent, gas plasma, FED, and/or other flat panel types." Dkt. No. 47, at 48. LG also relies on dictionary definitions to support distinguishing CRT display. LG urges that the specification's reference to a CRT display is in connection with prior art, and that "use of a flat panel display rather than a CRT \* \* \* is mandated by many of the goals of the invention." *Id.* at 50.

Hitachi argues that both parties "rely on extrinsic evidence that defines a flat panel display by the depth of the display" but that LG impermissibly "seeks to define this term by exclusion, stating that it cannot include a CRT." Dkt. No. 48, at 16. Hitachi suggests that LG's construction is really an attempt to undermine Hitachi's Rule 3 disclosures, "presumably so that LGE can argue to a jury that the Court has *already decided* that any distinction between a CRT and a flat panel display is significant and relevant in terms of the invalidity of claim 21." *Id*.

In response, LG argues that Hitachi ignores (1) "the express and limiting language in the preamble of the claim which recites a 'system for controlling the size, position and orientation of a video image presented *on a flat panel display,*' " and (2) "the 'orientation' limitation in claim 21, which is clearly directed to solving problems unique to flat panel displays such as LCD displays." Dkt. No. 55, at 43. Finally, LG urges that Hitachi's "phrases 'package thickness' and 'a small fraction of are vague and undefined \* \* \* and would unnecessarily confuse the finder of fact." *Id*.

# (2) Construction

[5] The specification provides numerous examples of flat panel displays, "including LCD,

electroluminescent, gas plasma, and FED display systems." '096 Patent, col. 3, lines 7-8. The specification's only reference to a CRT, though, is in the Background of the Invention:

Still further, electronic control systems for flat panel displays are known which accommodate color to color, and color to monochrome processing of video signals. *See* U.S. Pat. Nos. 5,193,069; 5,293,485; and 4,922,237. While U.S. Pat. No. 5,193,069 refers to and claims a color to grey scale conversion, the patent fails to disclose how such a conversion is accomplished. U.S. Pat. No. 5,293,485 discloses a complex system which uses a color palette in supplying color signals to a *computer CRT*. The system cannot support NTSC, PAL or HDTV video formats. U.S. Pat. No. 4,922,237 discloses a character conversion only, and cannot perform color to monochrome conversions for graphics. Electronic control systems for flat panel displays also are known which accommodate one or more of PAL, HDTV, NTSC, and VGA RGB video signals in driving the display.

'096 Patent, col. 1, lines 34-48. The apparent distinction here is that a CRT cannot support certain video formats, not that CRTs are not "flat panel" displays. During prosecution, the examiner essentially repeated that in a first office action that otherwise largely concluded that the claims were allowable. *See* Dkt. No. 69, Exh. '096 Pages 51-100, at HCX AS 0015734 [Office Action of November 20, 1997] ("Zenda [U.S. Patent No. 5,293,485] discloses a complex system which uses a color palette in supplying [color] signals to a computer CRT, but the [system] does not support NTSC, PAL, or HDTV video formats."). The intrinsic record thus draws a distinction between CRTs and flat panel displays, *i.e.*, the applicant did not lump the two together. Both were known in the prior art.

In general, though, when a term is a term of art, the term is given its art-recognized meaning. Here, "flatpanel display" is a term of art. One technical reference simply defines this term as "[a]n electronic display in which a large orthogonal array of display devices, such as electroluminescent devices or light-emitting diodes, form a flat screen." McGraw-Hill Dictionary of Scientific and Technical Terms 770, 1437 (5th ed.1994), 817, 1522 (6th ed.2003). Another reference defines this term as "[a] very thin display screen used in portable computers and increasing as a replacement for a CRT with desktop computers." Random House Webster's Computer and Internet Dictionary 217 (3d ed.1999). Yet another source defines a "flat panel display" as "[a] type of display device where the depth is much less than a conventional cathode ray tube for the same image size. Various flat panel technologies, including LCDs and plasma panels are competing to produce reliable high-resolution color displays, both large and small." Dictionary of Computing 193 (4th ed.1996) (included in Dkt. No. 47, Exh. 5, at LG A-V 025317). A further reference provides the following definition for the disputed term: "An electronic display with a package thickness that is a small fraction of the display's height or length." The McGraw-Hill Illustrated Dictionary of Personal Computers 186 (4th ed.1995) (included in Dkt. No. 48, Exh. 4, at HCX AS 0192687). These definitions are consistent with how that term is used in the specification.

# Thus, the Court construes the term "flat panel display" to mean "a flat electronic screen, formed from an array of display devices that use liquid crystal, electroluminescent, gas plasma, or similar technologies."

# f) "column replicate control signal" & "row replicate control signal"

These phrases appear in claim 21 (the disputed phrases are in boldface):

21. A system for controlling size, position and orientation of a video image presented on a flat panel

display, \* \* \* which comprises:

timing control means receiving said video signal from said video source at a video signal data rate for generating therefrom enable, vertical synchronization, horizontal synchronization, and first clock signals for driving said flat panel display, generating column start, row start, **column replicate**, and **row replicate control signals** for sizing said video image while maintaining a video signal resolution, and generating first control signals for reading said video image in said memory system;

image size/position control means in electrical communication with said timing control means and responsive to said column start, row start, **column replicate**, and **row replicate control signals** and said first control signals for generating output column address control signals, output row address control signals for said memory system, and a pixel clock signal; and

frame buffer output control means \* \* \*.

'096 Patent, col. 31, line 59-col. 32, line 19 (emphasis added).

#### (1) The Parties' Positions

The parties propose the following constructions:

| Phrase    | LG                                                                           | Hitachi                   |

|-----------|------------------------------------------------------------------------------|---------------------------|

| "column   | Signal that controls the number of times a particular column address         | An electronic signal that |

| replicate | identified at least in part by a column start control signal is read out of  | repeats an entire column  |

| control   | the frame buffer in order to control the size of video image on a display    | of pixels in the image.   |

| signal"   | screen.                                                                      |                           |

| "row      | Signal that controls the number of times a particular row address            | An electronic signal that |

| replicate | identified at least in part by a row start control signal is read out of the | repeats an entire row of  |

| control   | frame buffer in order to control the size of video image on a display        | pixels in the image.      |

| signal"   | screen.                                                                      |                           |

See Dkt. No. 64, at 29.

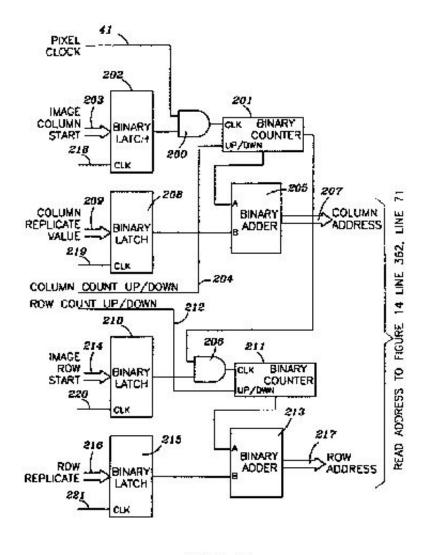

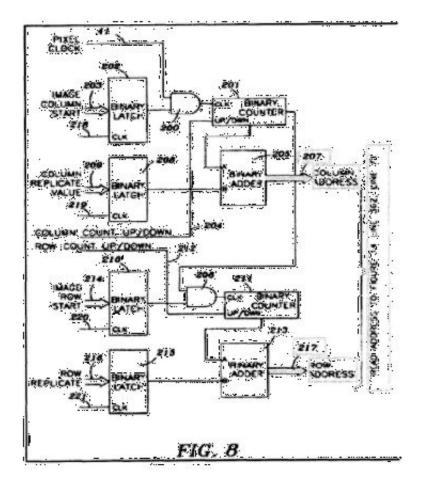

LG urges that "the dispute between the parties surrounds the nature of the claimed replicate signals and the corresponding description in the patent." Dkt. No. 47, at 50. According to LG, "the column or row of pixels in the image is not repeated, but rather, a particular column and row address is replicated." *Id.* LG contends that "[t]he specification describes that frame buffer output control unit 42 is programmed to access frame buffers 20, 24, and 25-in which a video image is stored-at a particular start column and start row memory address. In the case where no up-sizing or downsizing is to be performed prior to presenting the video image on a flat panel display, the frame buffer output control unit 42 continues reading the frame buffers according to the count up/down value." *Id.* at 51. LG urges that "the size of the video image to be displayed on the flat panel display may be changed by using horizontal and vertical replication" as "shown in Figure 8." *Id.* According to LG, "[t]he inputs to Figure 8 (i.e., image size/position control unit 39) include \* \* \* column and row replicate values [that] are used to re-size a video image." *Id.* LG argues that "in a simple example of resizing a video image horizontally, a primary column address is determined based on the image column start value on line 203 and a clock on line 218. The primary column address is applied to one input of the adder/subtractor 205. The replicate value then is added or subtracted from the primary column address as

determined by the sign of the replicate value. The resulting output of the adder/subtractor 205 is a column address which is applied to the frame buffer output control unit 42." *Id.* at 51-52. Thus, LG urges, "the column replicate value 209 represents a number of times a particular column address is read out of the frame buffer and the row replicate value 216 represents a number of times a particular row address is readout of the frame buffer," which in turn "controls the size of video image on a display screen." *Id* . at 52.

Hitachi argues that "the column replicate and row replicate signals control the number of times an *entire* column or row of pixels is repeated in the video image" and notes that "the only embodiment disclosed in the patent can replicate only an entire row or column of pixels, not an individual pixel or subsets of pixels within a displayed row or column." Dkt. No. 48, at 17. Hitachi also cites Figure 8, in noting that "the Column Replicate Value 209 and the Row Replicate Value 216 are values that are latched in respective Binary Latches 208 and 215 \* \* [and][t]hese latched values determine how many times an entire column or row of address signals is repeated as output Column Address signals 207 and output Row Address signals 217." *Id*. Finally, Hitachi urges that LG's constructions "only refer to replication of a particular pixel at a particular row and column address, rather than a complete row or column, \* \* [which] broaden[s] these terms so that they cover the situation where only a single pixel from within a row or column is replicated, but without replication of the complete row or the complete column that contains that pixel." *Id*. at 18.

In response, LG argues that the "specification does not require 'the column replicate and row replicate signals control the number of times an *entire* column or row of pixels is repeated in the video image' [but rather] the signals control the number of times a particular *column address* or *row address* is repeated in the video image and that the addressing can be commenced at *any location in the memory space*." Dkt. No. 55, at 43-44. LG urges that the example cited by Hitachi "is not discussing whether the *entire* row or column is repeated; instead, it is an example showing how to determine the Column Replicate or Row Replicate Factors, which merely calculate *which* nth row or nth column is repeated or skipped." *Id.* at 44. LG also notes that "the table above this passage clearly indicates that the start position for the row or column can fall anywhere between the ranges of 0 and 2047." *Id.*

#### (2) Construction

[6] [7] There is no dispute that this phrase refers to a signal; rather, the parties dispute what this signal does. The claim terms themselves suggest what they are for, *i.e.*, controlling column/row replication. Those words suggest what Hitachi urges, *i.e.*, that the columns and rows are replicated. According to the specification, the number of times that a column or row is repeated depends on the image size parameters set at the "image size/position control unit 39" (Figure 1). FN2

FN2. See supra Part II. A for a reproduction of Figure 1.